The design and manufacture of MEMS is very different and in many ways more complex process than even the most advanced ICs. MEMS involve multiple degrees of freedom (i.e. the device to exhibit different characteristics under different physical state, motion or mechanics), making fabrication of MEMS extremely complex; and hence… Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More2014: Keep calm, and program gates

I was tempted to call this piece “if you’re not using an FPGA, you’re doing it wrong,” but that didn’t quite capture the whole picture. Social memes aside, the FPGA as we know it is undergoing a serious transformation into a full blown SoC, and 2014 is the year that will usher in one of the biggest changes in the history of embedded design.… Read More

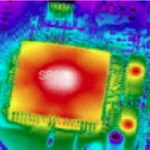

Early Thermal and Power Simulation Using Virtual Prototyping for Pedestrian Detection Applications

In the 1970’s we designed ICs first and when silicon came back then we measured the power and junction temperature. At that time there were no EDA simulation tools or models for full-chip power and temperature analysis. Fast forward to 2013 and we find that temperature and power are still demanding requirements for MPSoC … Read More

Will You Take the Password Pill?

As smartphone and tablet makers desperately search for points of differentiation they will try to push the limits of performance on several fronts to extremes. The password pill and the display-cover display are two of the stranger extreme features on the way.

Extreme inter-connectivity is one of the more useful features that… Read More

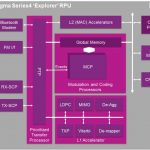

Raised on radio: RPUs target autos and wearables

We’ve become familiar with Imagination Technologies as a leading provider of IP for mobile GPUs, and within the last year the acquisition of the MIPS architecture has established them further in NPU and SoC circles. Their latest move targets an IP solution more in line with their heritage.

Imagination, way before becoming famous… Read More

Intel Wafer Pricing Exposed!

One of the big questions on Intel’s foundry strategy is: Can they compete on wafer pricing? Fortunately there are now detailed reports that support what most of us fabless folks already know. The simple answer is no, Intel cannot compete with TSMC or Samsung on wafer pricing at 28nm, 20nm, and 14nm.

In fact, recent reports have shown… Read More

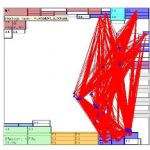

Macro Placement Challenges

One of the challenges of physical design of a modern SoC is that of macro placement. Back when a design just had a few macros then the flooplanning could be handled largely manually. But modern SoCs suffer from a number of problems. A new white paper from Mentor covers Olympus-SOCs features to address these issues:

- As we move to smaller

Get into a Xilinx FPGA for Under $90

Jump into Xilinx Programmable Logic today! I wanted to encourage my dear readers if you have not tried using an Xilinx FPGA (Field Programmable Gate Array) or even CPLD (Complex Programmable Logic Device) then it is worth your time to begin your evaluation. Maybe you got one for Christmas? If not, it is easier than you think to start… Read More

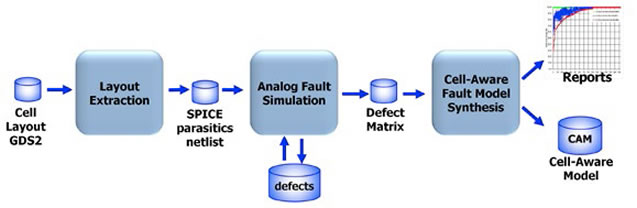

Patterns looking inside, not just between, logic cells

Traditional logic testing relies on blasting pattern after pattern at the inputs, trying to exercise combinations to shake faults out of logic and hopefully have them manifested at an observable pin, be it a test point or a final output stage. It’s a remarkably inefficient process with a lot of randomness and luck involved.

Getting… Read More

Smart Watch, Phone, Phablet, Tablet, Thin Notebook…?

There are more, but wait a while, from this set which ones do you need? Or let me ask the question differently (I know you may like something impulsively and have money to buy), which ones do you want to buy and own? Still confused? I guess what you need, you already have, but you want to change it for something new and different. While I … Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!