Since a few years, I have been following up Ansys Apachetools for semiconductor design, verification and sign-off. RedHawk is the most prominent platform of tools from Ansys, specifically for Power, Noise and Reliability Sign-off. It has witnessed many open endorsements from several of Ansyscustomers through open presentations,… Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreUnderstanding QoR in FPGA synthesis

We’ve all heard this claim: “Our FPGA synthesis tool produces better quality of results (QoR).” If you’re just hoping for a tool to do that automagically, you’re probably doing it wrong. Getting better QoR depends on understanding what an FPGA synthesis tool is capable of, and how to leverage what it tells you.… Read More

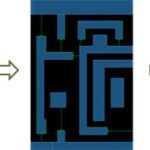

DRM2PDK: From design rule manual to process design kit

Exactly a year ago Sage Design Automation launched its revolutionary iDRM product, enabling for the first time to graphically capture design rules and compile them into checks automatically – no programming required. Using the graphical design rule editor, users could draw the layout topology that describes the design… Read More

Two New ESL Tools for Power and Thermal at DAC

Gary Smith published a list of what to see at DAC, and I noticed that he listed DOCEA Power in a category of ESL Thermal. I’ll be meeting the DOCEA engineers on Wednesday at DAC to learn more about their two newest ESL products:

- Thermal Profiler

- Power Intelligence

In general DOCEA Power tools allow you to manage power and thermal… Read More

Different Approaches to System Level Power Modeling and Analysis for Early Design Phases

At DATEthis year in Dresden, Bernhard Fischer from Siemens CT(Corporate Technology) has presented an interesting summary of the various techniques used for power modeling and analysis at the architectural level. He went through the pros and cons of using spreadsheets, timed virtual platforms annotated with power numbers … Read More

The Chip Design Game at the End of Moore’s Law

I just came across and interesting video from last year’s Hot Chips conference. Dr. Robert Colwell of DARPA discusses how the processor design industry is likely to change after it becomes too difficult to continue scaling transistors to ever-smaller dimensions. This is likely to occur sometime within the next decade,… Read More

SEMICON West 2014 Preview

There is a really big conference coming up in San Francisco…no, not DAC although of course that is coming up too. I’m talking about SEMICON West which is much bigger, filling all 3 Moscone exhibit halls. It is July 8-10th. It is, of course, the semiconductor equipment industry (and solar) show.

The opening keynote on… Read More

Mark Milligan Joins Calypto. Plus Google at DAC

I talked to Mark Milligan this morning, who has just joined Calypto as VP Marketing. I first met Mark back when he was at CoWare and I was at VaST or maybe it was Virtutech. Then he moved on and ran marketing at SpringSoft which, I’m sure you remember, Synopsys acquired. I asked him what encouraged him to join Calypto.

He said that… Read More

Methodics @ #51DAC!

This is the biggest year ever for Methodics at DAC, with lots to show, and a team of people excited to talk to customers and potential customers alike. Methodics will also be giving away Pebble Smartwatches!

Methodics theme for DAC2014 is “IP and design management done right”. A key part of this message is to show how their unique open… Read More

Dark Silicon

One of the problems with chips today is that of so-called “dark silicon”. We can put massive functionality on an SoC today. A billion transistors, and that is just at 28nm. But power constraints (both leakage and dynamic power) limit how much of the chip can be powered up at any one time. In some cases this is not that big… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center