Next week it is Semicon West, the big equipment vendor tradeshow. I love to go since EDA and semiconductor and all the stuff we are interested in here at Semiwiki are driven by equipment capabilities, especially lithography. The highest viewed blogs I write tend to be ones on technologies that are just a bit out beyond the stuff people… Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read MoreIt’s Always Good If the Customer Is Arguing

I’ve never been in sales. Never “carried a bag”. But I have run sales forces and I have spent a lot of time in marketing, guiding sales forces. Well, herding cats comes to mind, but cats don’t have commission plans. Engineers say sales people are emotional, and ego-driven, but change their commission plans… Read More

Intel is Speaking @ SEMICON West 2014!

The SEMICON West website has a nice “speakers” option where you can search by company and see who is talking about what. I’m always interested in what Intel has to say (they are still the leading semiconductor company) so here is the line-up for next week:

Intel Sanchali Bhattacharjee Subcomponent Supply Chain for 10nm and Beyond… Read More

In Case You Missed #51DAC

This will probably end up being the most memorable DAC for us since Paul and I signed hundreds of copies of our book “Fabless: The Transformation of the Semiconductor Industry”. I’m not sure how we are going to top that next year but I’m confident we will think of something. If you want to catch up on the live blogs from the last three conferences… Read More

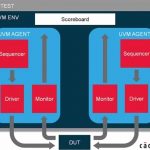

So Easy To Learn VIP Integration into UVM Environment

It goes without saying that VIPs really play a Very Important Part in SoC verification today. It has created a significant semiconductor market segment in the fabless world of SoC and IP design & verification. In order to meet the aggressive time-to-market for IPs and SoCs, it’s imperative that readymade VIPs which are proven… Read More

Analog FastSPICE Update at DAC

Tuesday night over dinner at DAC I was able to chat with Ravi Subramanian, CEO of Berkeley DA, recently acquired by Mentor Graphics back on March 21st. This acquisition provided Mentor with an Analog FastSPICE circuit simulator to round out its collection of simulators.… Read More

Is this thing real? Symmetric authentication will tell you!

The act of authentication is very straightforward. Essentially, it is making sure that something is real.

There are two parts to authentication:

[LIST=1]

Authentication in the “crypto-verse” typically happens on a host and client basis where the host wants to ensure that a client is

A song of optimization and reuse

If you hang around engineers for any time at all, the word optimization is bound to come up. The very definition of engineer is to contrive or devise a solution. With that anointing, most engineers are beholden to the idea that their job is creating, synthesizing, and perfecting a solution specifically for the needs of a unique situation.… Read More

PCI Express 4 specification just released for PCI-SIG DevCon

I have been alerted by a blog from Moshik Rubin from Cadence: PCI-SIG has finally released the PCIe 4.0 rev 0.3 specification for members’ review, on time for the PCI-SIG developers conference last June in Santa Clara. Since the early days of PCI Express in 2005, Denali (at that time, now Cadence) has positioned the PCIe VIP… Read More

RTL Signoff Update from #51DAC

In the early days of Customer Owned Tooling (COT) the signoff was done at the GDS II, or physical level. Today, however we see the trend of RTL signoff instead because of the EDA tools and methodology available. At DACearlier this month I met with Piyush Sanchetiof Atrenta to get an update on what’s new with RTL signoff.… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era