Thanks to the recent acquisition of Riviera Waves, CEVA is expanding from Digital only DSP IP, to supporting complete solution (Digital + mixed-signal) for both WiFi and Bluetooth functions. Such a move is already a very good market positioning, as customers prefer buying to a single source the digital and the mixed-signal part… Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read MoreEDA Mergers & Acquisitions Wiki Now Includes IP

When I started collecting my list of EDA mergers and acquisitions about 30 years ago, my objective was simply to determine the number of logos each EDA company owns. For that reason, I collected all the fish-eat-fish-eat-fish…. mergers and acquisitions, going way back to the very early days of EDA (even before it was called EDA).… Read More

Intel 14nm Delayed Yet Again?

This week I’m at SEMICON West with 27,000 of my closest friends. Good information, good networking, and some great rumors this year. Yesterday I heard a juicy rumor in the halls that Intel is still having 14nm yield problems. Remember, we heard a similar rumor last year and it turned out to be true. I Googled around this morning and … Read More

Bob Metcalfe Keynote at #semiconwest

My PhD is in distributed file systems so one of the key networking papers was Metcalfe and Boggs, 1976. It was titled Ethernet: Distributed Packet Switching for Local Computer Networks. This was the paper that introduced the world to Ethernet and to Bob Metcalfe. He was on stage yesterday here at Semicon West to give the afternoon… Read More

Are iPhones to Die For?

First there were car phones and admittedly I waited in line to get one when they went mainstream. It was a Motorola something or other and it came with a curly antenna for the back window. From there I got a Nokia, a flip phone, a BlackBerry, and now iPhones. These life changing devices would not have happened without the fabless semiconductor… Read More

Chip side of the Open Interconnect Consortium

Maybe it’s my competitive analysis gene, or too many years spent hanging out with consortium types, but I’m always both curious and skeptical when a new consortium arises – especially in a crowded field of interest. The dynamics of who aligns with a new initiative, and how they plan to go to market compared to other entities, prompts… Read More

Mark Adams Keynote at #semiconwest

The first surprise of the opening keynote for Semicon West was on the slides that were cycling on the screen as the room filled up. Somehow our book Fabless had managed to be in the rotation.

The opening keynote was by Mark Adams, the President of Micron. He was talking about upcoming big changes in the semiconductor environment, although… Read More

The Internet of Things @ SEMICON West 2014!

Clearly I’m a fan of IoT in regards to the future of the fabless semiconductor industry. The fabless semiconductor transformation unleashed all sorts of innovation giving us the SoC and the life changing mobile devices SoCs enable. Unfortunately modern SoC design is expensive and raising capital for semiconductor start-ups… Read More

Take a drive on the IoT with V2V

What platform has become the most sophisticated and intimate personal electronic environment ever? The car. To paraphrase a famous automotive company’s top executive, car companies are transforming the car into a powerful smartphone that allows drivers to carry around, customize, and interact with their digital world. Automotive… Read More

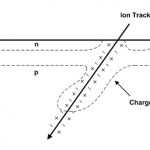

Modeling and Analysis of Single Event Effects (SEE)

Single Event Effects (SEE) are important because we depend upon our consumer, industrial and aerospace products to work reliably. Protons, electrons, neutrons, or alpha particles may perturb the MOS or bipolar device operation in either a destructive or non-destructive fashion. Galactic cosmic rays are one source of these… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry