Years ago I thought that chip design companies would embrace the latest technology and be eager to adopt new tools. What I learned was that the people implementing and managing design projects were taking a lot of risks with almost every aspect of their projects. What they most wanted is to minimize risk from the design process – especially… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More5 Verification Challenges of IoT Solved by Emulation

Software-centric Emulation environment takes the forefront in modern SoC verification. As more and more devices are IoT enabled, the SoCs have to make special provisions to factor many things including communication, power usage, and network switching, and so on. Also, the demand for an SoC (specifically for smartphone which… Read More

Cadence Enters the RTL Power Estimation Game

At the Cadence front-end summit last week, Jay Roy presented the Cadence Joules solution for RTL (and gate-level) power estimation. Jay is ex-Apache, so knows his way around RTL power estimation which should make Joules a product to watch. Joules connects very natively to Palladium for power characterization for realistic software… Read More

New Book: Mobile Unleashed!

This is the origin story of technology super heroes: the creators and founders of ARM, the company that is responsible for the processors found inside 95% of the world’s mobile devices today. This is also the evolution story of how three companies – Apple, Samsung, and Qualcomm – put ARM technology in the hands of billions of people… Read More

The Twists and Turns of Xilinx vs Altera!

The battle between Xilinx and Altera continues to be one of the more interesting stories to cover. It really is the semiconductor version of a reality TV show. In the beginning it was two fabless companies partnered with rival foundries going head-to-head controlling a single market that touches a variety of industries.

Then things… Read More

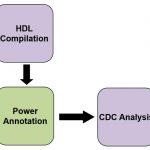

Syncing Up CDC Signals in Low Power Designs

So far in my blog series on low power we’ve looked broadly at what’s changing in the low power verification landscape and focused on a new methodology developed by Mentor Graphics and ARM called successive refinement, which is now included in the UPF standard. Power management techniques create their own brand of clock domain crossing… Read More

Intellectual Ventures Patents for Internet of Things (IoT)

More than 15,000 Intellectual Ventures’ US issued patents and published patent applications are reviewed for finding the good candidates for the IoT strategically packaged patent portfolio. Even if the Internet of Things (IoT) gets a huge attention recently, the concept of interconnected devices and connecting billions … Read More

Evolution of Non Volatile Memory for Sensitive Data

When first interested in computers while I was in junior high school in the early 70’s I remember seeing a core memory board for the first time. It was a seriously large circuit board with a myriad of wires woven across it going through the tiny metal doughnuts that stored the bit values. The computers it went into only had a total of around… Read More

CEVA Royalty Revenues in 2015 Supports Future IoT Design Win

DSP IP addressing modem for the mobile phone market is still the flagship product and CEVA enjoys design-win at major semiconductor account (one of them being vertical and also selling the smartphone), but the acquisition of Riviera Waves in 2014 has been a strong sign of diversification. CEVA’ port-folio includes signal processing… Read More

Optimizing power for wearables

I was at the Cadence front-end summit this week; good conference with lots of interesting information. I’ll start with a panel on optimizing power for wearables. Panelists were Anthony Hill from TI, Fred Jen from Qualcomm, Leah Clark from Broadcom and Jay Roy from Cadence. Panels are generally most entertaining when the panelists… Read More

Solving the EDA tool fragmentation crisis