It is an indictment of our irrationality that our cars are now more health-conscious than we are. Increasingly safety-conscious readings of the ISO26262 standard now encourage that safety-critical electronics (anti-lock braking control for example) automatically self-test, not just at power-on but repeatedly as the car… Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read MoreCalibre in the Middle of Semiconductor Ecosystem

Albert Einsteinhad said, “In the middle of difficulty lies opportunity”. In today’s world dominated by technology, or I must say internet which has initiated collaborative information sharing, “leading from the middle” is the new mantra of life.… Read More

The Cult of IoT! (FitBit)

Granted the word “cult” can have a negative connotation, especially when applied to small religious groups but cult can also mean a great devotion to a movement or intellectual fad. Some people call Apple a cult with Apple Stores being their Churches. If you look at the lines around the block or down the mall for new product… Read More

Variation Aware FinFETs are Critical!

As I mentioned in “EDA Dead Pool” acquisitions in our industry will continue at a rapid pace. The latest victim is 10 year old French company Infiniscale who was recently purchased by Silvaco. This was more of a “let’s put your product through our massive sales and support channel” kind of deal so it will be 1 + 1 = 3 accretive for sure.… Read More

IEDM Blogs – Part 3 – Global Foundries 22FDX Briefing

While I was at IEDM I had an opportunity to sit down with Subramani (Subi) Kengeri, the Vice President, General Management, CMOS Platforms Business Unit and Jason Gorss from corporate marketing at Global Foundries (GF) for a briefing on GF’s new 22FDX process technology.

Subi told me his background was in design but that he is now… Read More

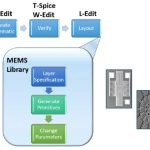

Mass customization coming to MEMS?

With the industry abuzz about the Apple purchase of a Maxim Integrated fab as a potential R&D facility for MEMS design, it begs the question: is creating a MEMS device that easy?

MEMS technology is approaching the same fork in the road where digital design encountered LSI four decades earlier. … Read More

Slinging Stones at the Data Center Semi Goliaths

For those not aware, there is quite a battle brewing in data center wired communication segment (across which most wireless data traffic traverses). A primary impetus driving the competitive positioning is the recent commercial availability of single lane 25 Gbps serdes (serializer / deserializer) channels in 28 nm CMOS from… Read More

Hyperloop: Faster Than the Shinkansen

In 1987 I made my first trip to Japan for business, then rode in my first high-speed train on the fabled Shinkansen (aka bullet train) traveling up to 200 mph on the way from Tokyo to Kyoto. Compared to the USA, our engineering friends in Japan have the most futuristic high-speed trains in the world. Today there’ s talk about another… Read More

What’s Driving Real Medical Tech

I just watched a webinar on non-invasive bio-imaging as a way to detect and track disease, which gave me a sense of the way tech progresses in the medical field and makes for a positive counterpoint to my views on medical IoT, at least as envisioned in much of our industry. The webinar, on new approaches to in-vivo imaging was hosted … Read More

Challenges in IP Qualification with Rising Physical Data

With every new technology node, there are newer physical effects that need to be taken into account. And every new physical effect brings with itself several new formats to model them. Often a format is also associated with several of its derivatives, sometimes an standard reincarnation of a proprietary format further evolved… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era