Over the past few years of being immersed in the Internet of Things (IoT), I have found that customers have very specific problems they are trying to solve; e.g. gaining energy efficiency, early fault detection or remote diagnosis and maintenance of equipment. Decisions are driven by the need to reduce Operational Expenditure… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreLow end LTE UE categories seeing more action

Most of our attention goes toward the higher end of the LTE UE categories – ones designed for moving large amounts of multimedia data from smartphones and tablets concurrently with voice traffic. An equally interesting discussion is taking shape at the low end of the LTE UE categories targeting M2M and IoT devices with power-efficient,… Read More

Sleep Monitoring and Aiding Devices Insight from Patents

US9192326 illustrates a sleep monitoring system that can be embodied within a wearable device or in a mobile device. The system includes an accelerometer to monitor a user’s movements. The system determines when the user is falling asleep into a sleep session based on the user’s movements. The system also identifies… Read More

Complexity And Security

From time to time when talking about security, it is useful to look at the big picture, but not to further lament the imminent collapse of the sky. We all know that the problem is big and we’re really not on top of it. A more productive discussion would be about what we can do to reduce the scope of the problem. And that has to start … Read More

Automotive Deaths and Big Data

Nothing focuses peoples’ attention quite as effectively as death and there’s been a lot of it on U.S. highways lately. Preliminary figures released this week by the National Highway Traffic Safety Administration (NHTSA) reveal that for the first nine months of 2015 traffic fatalities increased 9.3%.… Read More

IP Vendor Nabs Top Talent from Semiconductor Industry

The growth of mobile and IoT have helped increase the demand for One Time Programmable Non Volatile Memory (OTP NVM) as a solution for on-chip storage. To continue to meet this demand and grow with it, industry leading Sidense has recently brought on board seasoned semiconductor executive Ken Wagner as VP of Engineering. He was … Read More

Synopsys’ New Circuit Simulation Environment Improves Productivity — for Free

When technology advances, complexities increase and data size becomes unmanageable. Fresh thinking and a new environment for automation are needed to provide the required increase in productivity. Specifically in case of circuit simulation of advanced-node analog designs, where precision is paramount and a large number… Read More

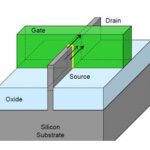

How 16nm and 14nm FinFETs Require New SPICE Simulators

About 35 years ago the first commercial SPICE circuit simulators emerged and they were quickly put to work helping circuit designers predict the timing and power of 6um NMOS designs. Then we had to limit our circuit simulations to just hundreds of transistors and interconnect elements to fit into the RAM and complete simulation… Read More

The Next Wave of Semiconductor Companies!

As we all know, venture capital has all but disappeared for semiconductor companies. Do semiconductor startups still exist and where do they come from? I ask these questions quite frequently but bloggable answers are hard to come by. When I asked Mike Gianfagna of eSilicon during ISSCC he reminded me of an old new source of emerging… Read More

Let’s Reduce Wasted Energy in Server Farms

With the growth in streaming video and the promises of 50 billion IoT gadgets making our lives oh-so-much better, there is an alarming demand for online computational horsepower and bandwidth.

Why alarming? In 2014, data centers in the United States consumed approximately 100 billion kilowatt hours (kWh) of energy. According… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era