2017 was a banner year for semiconductor sales as they topped $400B for the first time, an increase of some 20%, there is happiness in Silicon Valley, Taiwan, South Korea, and well, everywhere. With the foundries pushing to ever-smaller process dimensions and even going back to mature nodes and offering more variations that are… Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

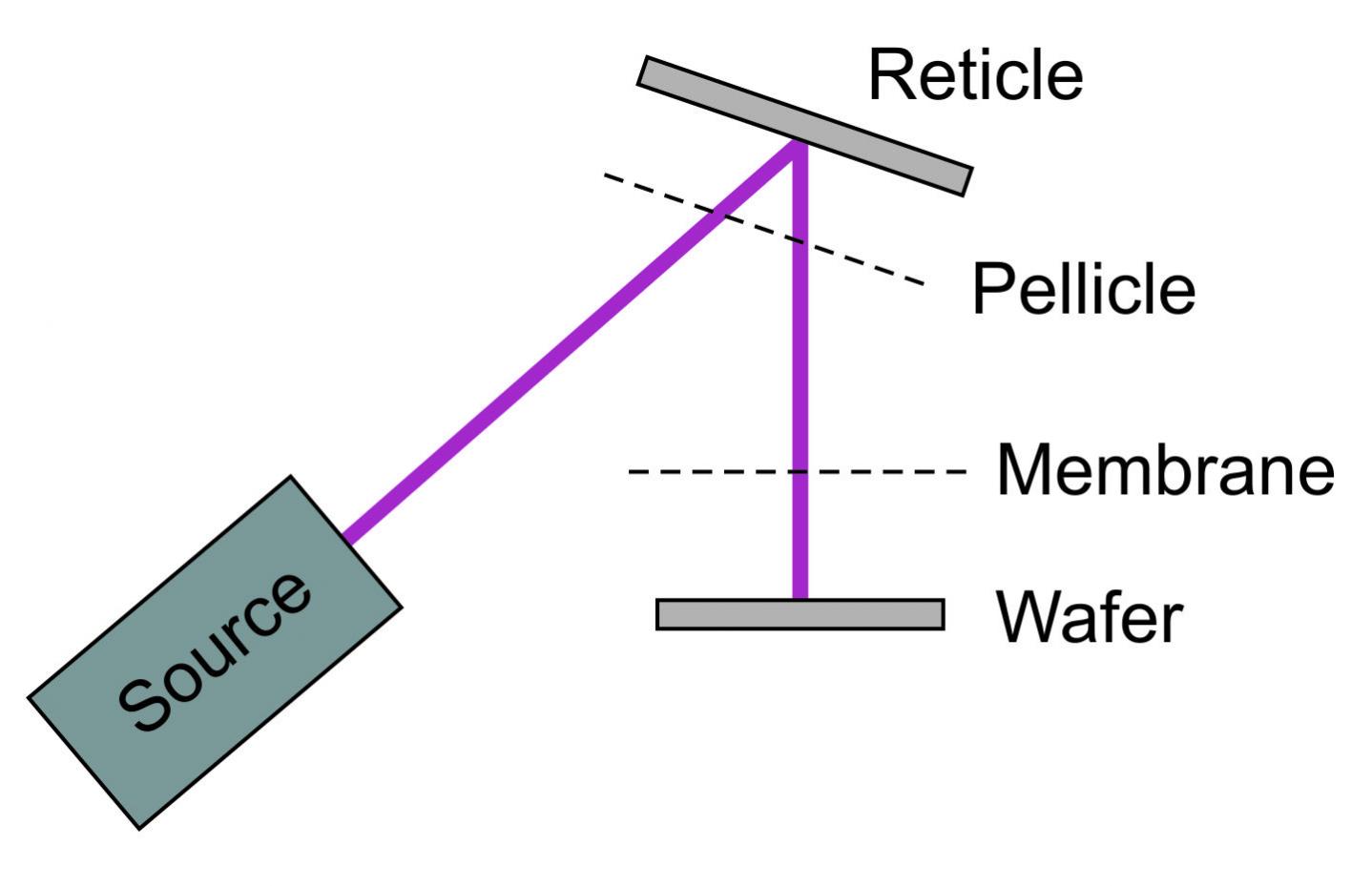

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreISS 2018 – The Impact of EUV on the Semiconductor Supply Chain

I was invited to give a talk at the ISS conference on the Impact of EUV on the Semiconductor Supply Chain. The ISS conference is an annual gathering of semiconductor executives to review technology and global trends. In this article I will walk through my presentation and conclusions.… Read More

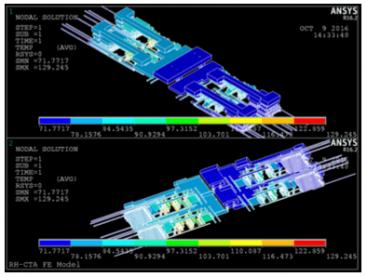

Thermal Modeling for ADAS goes MultiPhysics

In electronic system design, we have grown comfortable with the idea that different regimes of analysis, such as the chip, the package and the system, or electrical, thermal and stress are more or less independent – what starts in one regime stays in that regime, give or take some margin information passed onto other regimes. And… Read More

A Reliable Way to Forecast Growth of Semiconductor Markets

Wally Rhines, President and CEO of Mentor, a Siemens Group, did another one of his famous deep learning presentations at SEMI ISS 2018. Using the Gompertz Curve Lifecycle to forecast the future growth of semiconductor markets, Wally looks at: Image sensors, Desktop PCs, PC Notebooks, Cell Phone Subscribers, Smartphones, and… Read More

Mentor Tessent Products Ready for Second Edition of ISO 26262 Coming in March 2018

Have you notice how smart your automobile is getting? Watching the first round of NFL playoffs I lost count on the number of TV commercials showing cars weaving through tight construction zones (and Star Wars figures), big trucks parking in incredibly tight spaces, cars avoiding rear-end collisions and pedestrians, and even … Read More

A Golden Age for Semiconductor Growth at ISS 2018

The SEMI Industry Strategy Symposium (ISS 2018) started today with session one on economic trends. Daniel Niles (Alpha One Capital Partners) started it off with “A Golden Age for Global Growth – Semiconductor revenues up over 20% y/y (The Good News is Also the Bad News)”. The good news of course is that semiconductors continue… Read More

Scoreboard and Issues Management Tools for PCB Projects

The complexity of an SoC design necessitates that the project managers have accurate visibility into the overall design status, spanning the entire range of tasks – from functional simulation error triage, to physical layout verification errors, to electrical analysis results. Flow scripts used by SoC teams parse the log file… Read More

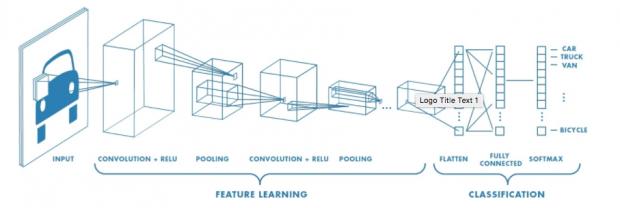

Better than CNN

No, not the news network though I confess I am curious to see how many initial hits that title attracts. Then I clarify that I’m talking about convolutional neural nets, and my would-be social media fame evaporates. Oh well – for those few of you still with me, CNNs in all their many forms are the technology behind image, voice and other… Read More

Moving from FPGA’s to Embedded FPGA Fabric – How it’s Done

Buying IP is just a little bit more complicated than buying a pair of shoes. A lot of IP is configurable and requires attention to various design and configuration parameters. We live in an age where commercial soft IP is used pretty often in designs, so people have developed increasing comfort in the process that is required to achieve… Read More

Broadcom Versus Qualcomm Update

The Broadcom acquiring Qualcomm drama is still dominating the fabless semiconductor back channel. This week I will be at the SEMI ISS Conference with Scott Jones and several hundred high level semiconductor professionals so it will be interesting to hear the hallway chatter. When it was first announced I was in the minority in … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center