The Design IP market is doing well, growing at higher CAGR that the semiconductor market it is serving, in fact 10% higher for 2007-2017! You may wonder why this IP market is so business friendly? I will try to answer and propose the top 3 reasons explaining this behavior. To name it: IP business is recurrent, external IP sourcing is… Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreProject Verification Planning for Analog Designs

Successful projects leverage the investment in comprehensive methodology and resource planning, covering design and analysis flows – that planning effort is especially important for functional verification.

The emergence of complex SoC designs for advanced automotive applications has led to a major focus on verification… Read More

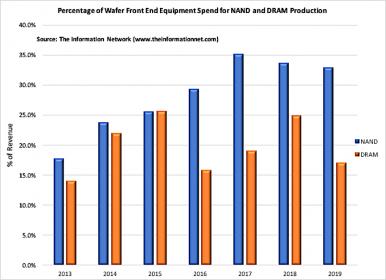

Doesn’t sound like a recovery anytime in 2019

AMAT reported a more or less in line quarter with revenues of $3.75B and Non-GAAP EPS of $0.81 versus street expectation of $0.79 and revenues of $3.71B. Guidance came in well below the street with revenues expected between $3.33B to $3.63B and Non-GAAP EPS from $0.62 to $0.70 versus expectations of $3.66B and $0.77. The company … Read More

Car Sharing Prophets and Losses

Industry analysts are fond of painting terrifying pictures of catastrophic market changes resulting from disruptive technologies or business models. Nowhere is this more evident, of late, than in the automotive industry where everything from artificial intelligence to automated driving is expected to upend current thinking… Read More

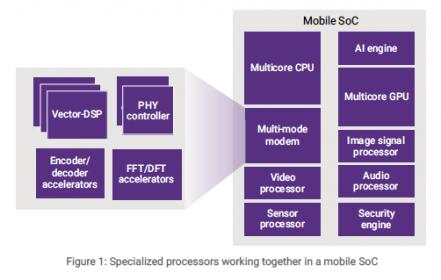

Goldilocks Solution for SOC Processors

SOC designers face choices when it comes to choosing how to implement algorithms in their designs. Moving them to hardware usually offers advantages of smaller area, less power and faster processing. Witness the migration of block chain hashing from CPUs to ASICs. However, these advantages can come with trade-offs. For one, … Read More

AI, Deep Learning, SystemC, UVM, PSS – DVCon Has it All

Today I had the pleasure to speak with Tom Fitzpatrick, TPC Chair for the DVCon conferenceand exhibition slated for February 25-28 in the heart of Silicon Valley – San Jose. Tom lives in Massachusetts, a place where I used to live and work at Wang Labs, back in the day before the PC and WordPerfect software ended Wang’s… Read More

Accelerating 5G Innovation and Reliability Through Simulation and Advanced FinFET Design

In an ANSYS seminar held at DesignCon 2019, Dr. Larry Williams, ANSYS Director of Technology, outlined how 5G design innovation can be accelerated through simulation. He posited that 5G will become a general-purpose technology that affects an entire economy, drastically alter societies and unleash a cascade of complementary… Read More

Semiconductor Equipment Companies Facing Significant Headwinds in 2019

In January 2019, the memory market has been hit with a significant amount of negative news.

- On Jan. 15, DRAM manufacturer Nanya Technology reported its Q4 2018 revenue was $551 million, down 30.4% QoQ.

- On Jan. 24, 2019, SK Hynix reported Q4 2018 earnings. Revenues fell 13.7% QoQ to $8.7 billion, while operating profit amounted to

Data Center Optimization Through Game Theory

I always enjoy surprising synergies so I was immediately attracted to a Research Highlight in the Communications of the ACM this month, on a game-theoretic method to balance discretionary speed-ups (known as computational sprints) in data centers. If you don’t have an ACM membership and want to dig deeper, I include an open link… Read More

Renaming and Refactoring in HDL Code

I’ve enjoyed my past discussions with Cristian Amitroaie, the CEO of AMIQ EDA, in which we covered their Design and Verification Tools (DVT) Eclipse Integrated Development Environment (IDE) and their Verissimo SystemVerilog Testbench Linter. Cristian’s descriptions of AMIQ’s products and customers have intrigued me. They… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center