As the number one 56thDAC supporting portal we will publish what’s happening in the conference, on the exhibit floor, and outside activities. The SemiWiki bloggers will be out in full force with live coverage and behind the scenes looks. Remember, SemiWiki bloggers are actual semiconductor professionals with hundreds… Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read MoreGetting to EMC Compliance by Design

At the risk of highlighting my abundant lack of expertise in the domain, I had always viewed EMC (electromagnetic compatibility) compliance and testing as one of those back-end exercises that can only be done on the real device and depends on a combination of expertise and brute-force in chip/package/module/system design (decaps,… Read More

Achieving a Predictable SignOff in 7nm

Designing with advanced-nodes FinFETs such as 7nm node involves a more complex process than prior nodes. As secondary physical effects are no longer negligible, the traditional margin-based approach applied at various design abstraction levels is considered ineffective. Coupled with the increase of device counts, failing… Read More

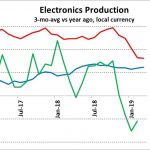

Trade war shifts electronics production

The U.S. is showing steady growth in electronics production. Three-month-average change versus a year ago (3/12) in March 2019 was 6.2%, the 12[SUP]th[/SUP] consecutive month of growth above 5%. China electronics production is decelerating, with March 2019 3/12 growth of 8.2%, similar to 8.3% in February. This marks the first… Read More

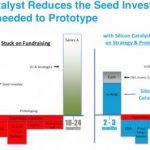

Re Energizing Silicon Innovation

Hardware is roaring back into prominence in technology innovation, from advanced cars to robots, smart homes and smart cities, 5G communication and the burgeoning electronification of industry, medicine and utilities. While software continues to play a role, all of these capabilities depend fundamentally on advances in … Read More

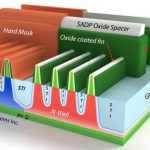

The Evolution of the Extension Implant Part V

Part 4 of this series discussed how a transistor Extension could be fabricated in a planar device without using an implant operation, and is instead formed using a preferential etch followed by a selective epitaxial deposition. This final installment of the series will present the formation of an Extension in a FinFET transistor… Read More

Uber’s Sandcastle

As Uber’s initial public offering arrives this is a good moment to consider what kind of employment model for the future we all, as employees and employers, would prefer to adopt: Amazon or Uber?

One of my sons has interviewed with Amazon. The other has his Amazon moment today. My across-the-street neighbor works for Amazon Web Services.… Read More

Chip Equip Trade War Collateral Damage

We have been very vocal and perhaps the first to warn of the risks to the semiconductor and semiconductor equipment industry from the China trade war with the US. It seems that the war is now fully upon us with the imposition of 25% tariffs by the US and promised retribution by China. The semiconductor industry is at the leading edge … Read More

The SiFive Tech Symposiums are Heading to Six Cities in Europe in May!

Hello Cambridge, Grenoble, Stockholm, Moscow, Munich and Amsterdam

Our 2019 global symposiums and workshops have been hugely successful in promoting the RISC-V ISA and fostering expansive collaboration within the open-source community. It’s invigorating to see how the worldwide semiconductor ecosystem is energized and… Read More

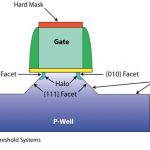

The Evolution of the Extension Implant Part IV

Perhaps the most innovative and effective Extension implant does not involve an implant at all, but is instead an etch followed by a selective epitaxial deposition.

In this Extension fabrication methodology the Source/Drains regions in a planar device are etched away in the normal fashion to accommodate the replacement Source/Drain… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry