These are stressful times in functional verification. We are being pushed to more aggressively embrace AI-based automation, knowing we will continue to be held accountable for quality of results. Verification misses could upend careers, maybe enterprises. It is tempting to believe that sanity will prevail and we will ultimately… Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreScaling Multi-Die Connectivity: Automated Routing for High-Speed Interfaces

This article concludes the three-part series examining key methodologies required for successful multi-die design. The first article Reducing Risk Early: Multi-Die Design Feasibility Exploration focused on feasibility exploration and early architectural validation, while the second article Building the Interconnect… Read More

Beyond Moore’s Law: High NA EUV Lithography Redefines Advanced Chip Manufacturing

The imec installation of the ASML EXE:5200 High Numerical Aperture (High NA) extreme ultraviolet (EUV) lithography system at imec represents a pivotal advancement in semiconductor manufacturing and research. This system, installed in imec’s 300 mm cleanroom in Leuven, Belgium, introduces unprecedented lithographic resolution… Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet Summit

At the recent Chiplet Summit, presentations, discussions and general participation could be broken down into a few broad categories. There were presentations of actual chiplet designs, either as building blocks or end products. There were presentations regarding design tools and methodologies to support and accelerate … Read More

CEO Interview with Moti Margalit of SonicEdge

Moti Margalit is the CEO and co-founder of SonicEdge, a deep-tech pioneer reinventing sound through ultrasonic modulation – unlocking smaller, vibration-free speakers with studio-quality audio.

With a background in lasers and electro-optics, Moti transitioned from technologist to inventor. His career spans 150+ patents… Read More

Podcast EP336: How Quadric is Enabling Dramatic Improvements in Edge AI with Veer Kheterpal

Daniel is joined by Dr. Veer Kheterpal. Veer has founded three technology companies and possesses full-stack expertise spanning software to silicon across edge and datacenter applications. Currently, he is the CEO & co-founder of Quadric, a semiconductor IP licensing company that delivers the blueprints for efficient,… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?

Intel has posted three consecutive years of falling revenue and an $18.76 billion loss in 2024 alone—and the U.S. government has handed it tens of billions of dollars to fix the problem. The government money isn’t fixing the real issue, which isn’t technical. It’s cultural. Intel got slow, political, and risk-averse—the… Read More

WEBINAR: Reclaiming Clock Margin at 3nm and Below

At 3nm and below, clock networks have quietly become the dominant limiter of SoC power, performance, and yield. Yet most advanced-node designs still rely on abstraction-based signoff methodologies developed when voltage headroom was generous and interconnect effects were secondary.

That assumption no longer holds

As supply… Read More

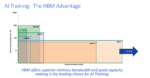

WEBINAR: HBM4E Advances Bandwidth Performance for AI Training

The rapid proliferation of LLMs and other AI applications, and of high-end GPU platforms that run them, is putting intense pressure on the performance requirements for memory technologies. Designers need to be keenly aware of how to make the most of their memory and controller choices, which can be moving targets given the rapid… Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design Enablement

The recent Chiplet Summit in Santa Clara was buzzing with new designs and new design methods. It felt like the industry had turned a corner at this year’s event with lots of new technology and design success on display. Siemens EDA had a large presence at the show and took home the Best in Show Award for Packaging Design. There were a … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center