Automotive electronics bring strong demand for power management chips, but its strict reliability requirements also pose new challenges for chip designers. The chip needs to be able to work in various harsh environments such as high temperature, low temperature, aging, abnormal power supply, etc. Although the traditional… Read More

Perforce and Siemens Collaborate on 3DIC Design at the Chiplet SummitThe recent Chiplet Summit at the Santa Clara…Read More

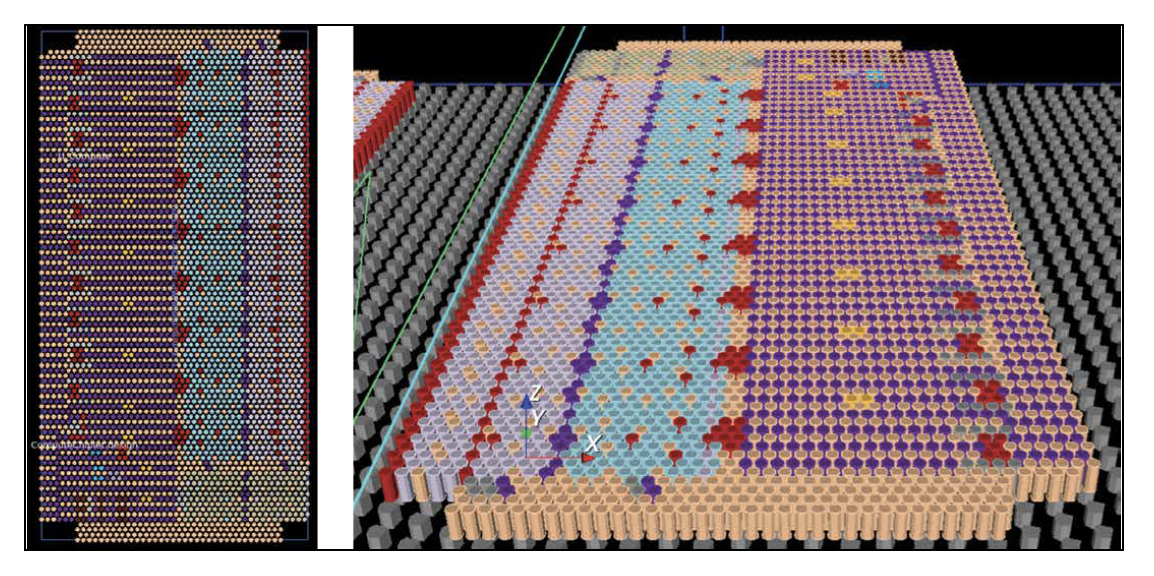

Perforce and Siemens Collaborate on 3DIC Design at the Chiplet SummitThe recent Chiplet Summit at the Santa Clara…Read More Building the Interconnect Foundation: Bump and TSV Planning for Multi-Die SystemsThe first article in this series examined how…Read More

Building the Interconnect Foundation: Bump and TSV Planning for Multi-Die SystemsThe first article in this series examined how…Read More CHERI: Hardware-Enforced Capability Architecture for Systematic Memory SafetyThe rapid escalation of cyberattacks over the past…Read More

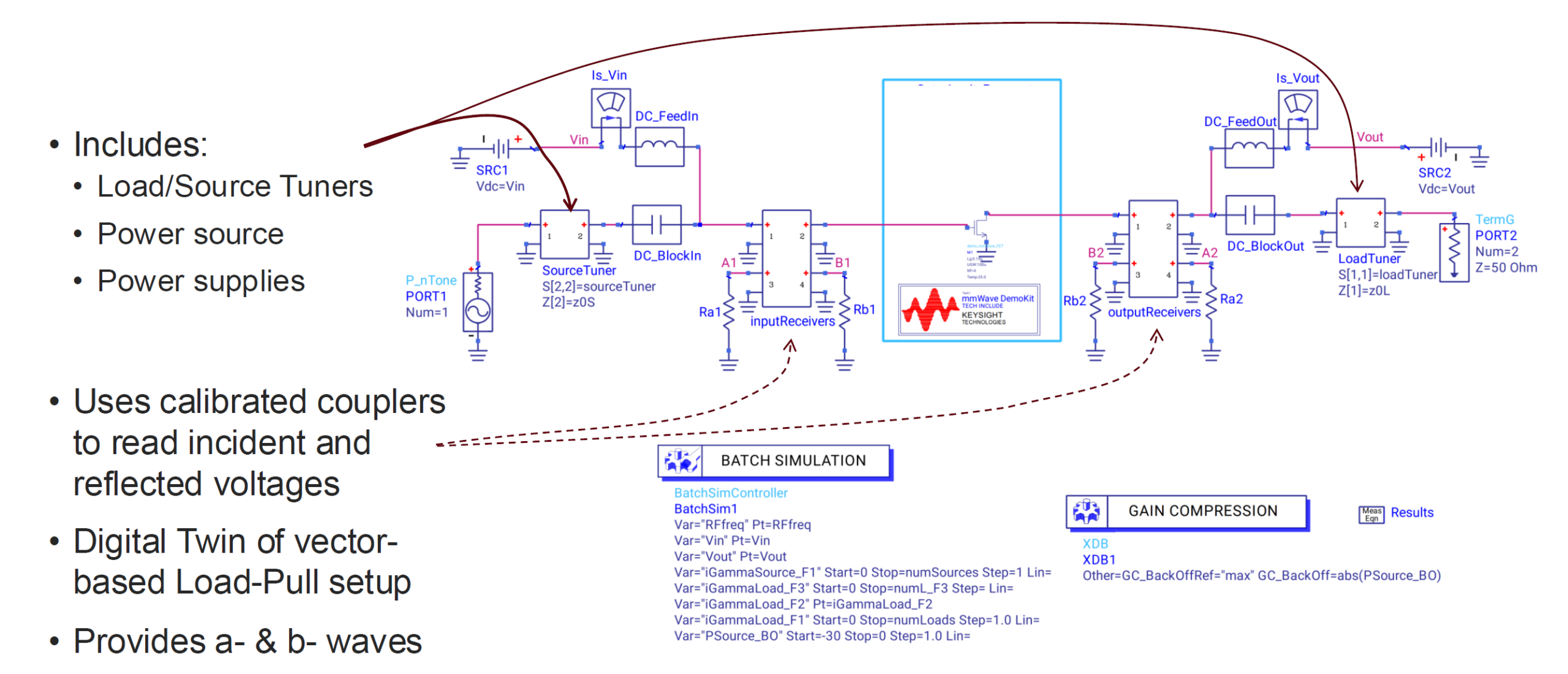

CHERI: Hardware-Enforced Capability Architecture for Systematic Memory SafetyThe rapid escalation of cyberattacks over the past…Read More WEBINAR: Two-Part Series on RF Power Amplifier DesignAt lower frequencies with simpler modulation, RF power…Read More

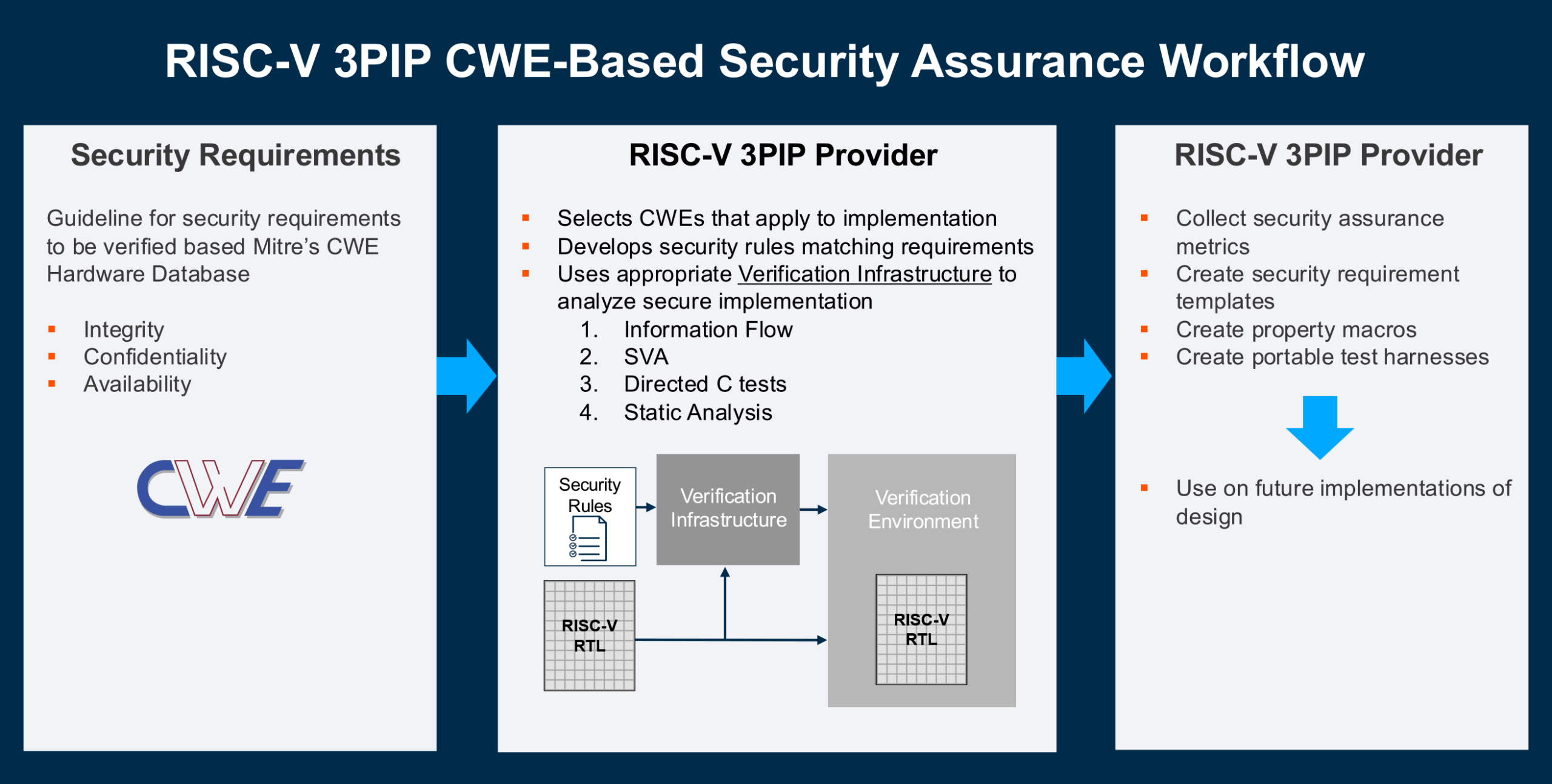

WEBINAR: Two-Part Series on RF Power Amplifier DesignAt lower frequencies with simpler modulation, RF power…Read More Securing RISC-V Third-Party IP: Enabling Comprehensive CWE-Based Assurance Across the Design Supply Chainby Jagadish Nayak RISC-V adoption continues to accelerate…Read More

Securing RISC-V Third-Party IP: Enabling Comprehensive CWE-Based Assurance Across the Design Supply Chainby Jagadish Nayak RISC-V adoption continues to accelerate…Read MoreHardware Data Acceleration for Semiconductor Design

This blog is a follow-on piece to an earlier one titled NetApp’s ONTAP Enables Engineering Productivity Boost. If you have not had an opportunity to read that blog, please do so for context. Using real life examples, it showcases how customers could improve real-world design engineering productivity as much as 10%.

For the … Read More

IAA Mobility: The Un-Car Show

IAA Mobility held in Munich last month was the first post-pandemic international auto show to take place outside of China. The organizers positioned automotive displays in city-center plazas while car companies rubbed shoulders with large suppliers and tiny startups on the show floor at the conference center.

Attendees would… Read More

Podcast EP42: Semiconductor Materials Innovations

Dan is joined by Alex Yoon, head of strategic and emerging technologies at Intermolecular. Dan and Alex explore the application of Intermolecular’s materials research capabilities, including their prototype fab in the Bay Area.

The views, thoughts, and opinions expressed in these podcasts… Read More

CEO Interview: Mike Wishart of Efabless

Mike Wishart has a storied career in investment banking and technology. His resume includes stints at Smith Barney, Lehman Brothers and Goldman Sachs after his Stanford MBA. He has served as a director at Brooktree, Spansion, Cypress and now Knowles. Mike is also a venture partner at Tyche Partners, a venture capital firm focused… Read More

DARPA Toolbox Initiative Boosts Design Productivity

When you think of the Defense Advanced Research Projects Agency (DARPA), this first thing that comes to mind is the development of the internet. And indeed, if you look at their website’s historic timeline, the development of ARPANET, as it was known at the time, is shown prominently in 1969. Incidentally, I actually used one of … Read More

Semiconductors – Limiting Factors; Supply Chain & Talent- Will Limit Stock Upside

– If chips are “as good as it gets” so are the stock prices

– Are we at a near term ceiling that stocks have bounced off of?

– If growth slows do valuations also slow?

– Are we in a holding pattern waiting for a down cycle?

Second order derivative investing

As we have said many times in the past, investors… Read More

Podcast EP41: A First Look at DAC 2021

Dan and Mike are joined by Harry Foster, Chief Scientist Verification at Siemens Digital Industry Software, Co-Founder and Executive Editor for the Verification Academy and 2021 Design Automation Conference General Chair. In this first in a series of DAC podcasts, we explore several dimensions of DAC 2021 with Harry, including … Read More

IBM and HPE Keynotes at Synopsys Verification Day

I have attended several past Synopsys verification events which I remember as engineering conference room, all-engineer pitches and debates. Effective but aiming for content rather than polish. This year’s event was different. First it was virtual, like most events these days, which certainly made the whole event feel more… Read More

Blur, not Wavelength, Determines Resolution at Advanced Nodes

Lithography has been the driving force for shrinking feature sizes for decades, and the most easily identified factor behind this trend is the reduction of wavelength. G-line (436 nm wavelength) was used for 0.5 um in the late 1980s [1], and I-line (365 nm wavelength) was used down to 0.3 um in the 1990s [2]. Then began the era of deep-ultraviolet… Read More

CEO Interview with Jerome Paye of TAU Systems