Dan is joined by Malcolm Penn, founder and CEO of Future Horizons, a firm that provides industry analysis and consulting services on the global semiconductor industry.

Dan and Malcolm discuss the current and future state of the semiconductor industry. What has driven the cyclic nature of the business and are we doomed to repeat… Read More

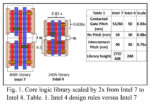

As I previously wrote about here, Intel is presenting their Intel 4 process at the VLSI Technology conference. Last Wednesday Bernhard Sell (Ben) from Intel gave the press a briefing on the process and provided us with early access to the paper (embargoed until Sunday 6/12).

“Intel 4 CMOS Technology Featuring Advanced FinFET Transistors… Read More

Dan is joined by Sharad Chole, chief scientist & co-founder at Expedera. Sharad is an expert in AI frameworks, power-aware neural network optimizations, and programmable dataflow architectures. Previously, he was an architect at Cisco, Memoir Systems, and Microsoft.

Dan and Shared explore Expedera’s unique AI… Read More

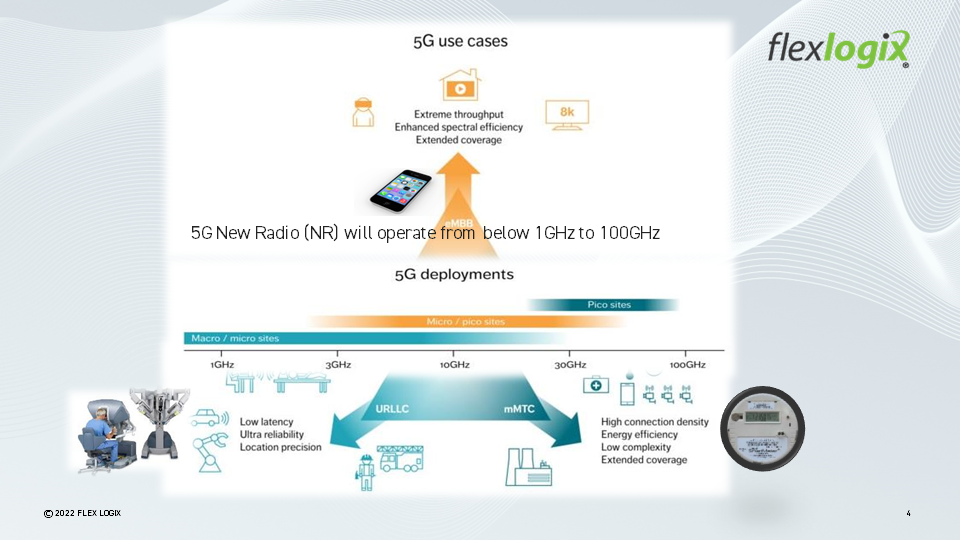

The demands of 5G requires new designs to not only save power but also increase performance and by moving to advance power-saving nodes and by using eFPGAs will help to achieve these goals. This paper will introduce 5G and O-RAN, the complexity of these systems, and how flexibility could be beneficial. Then we will dive into how eFPGA… Read More

The emergence of 2.5D packaging technology for heterogeneous die integration offers significant benefits to system architects. Functional units may be implemented using discrete die – aka “chiplets” – which may be fabricated in different process nodes. The power, performance, and cost for each unit may be optimized separately.… Read More

SLAM – simultaneous localization and mapping – is already a well-established technology in robotics. This generally starts with visual SLAM, using object recognition to detect landmarks and obstacles. VSLAM alone uses a 2D view of a 3D environment, challenging accuracy; improvements depend on complementary sensing inputs… Read More

Dan is joined by semiconductor and EDA industry veteran Douglas Fairbairn. Doug provides details about MegaChips, where he currently heads business development. MegaChips is a large, successful 30-year old semiconductor company based in Japan.

Doug is helping MegaChips launch in the US with a focus on ASIC design and delivery.… Read More

In sports, we’re all familiar with how even a team with the best individual players for every role needs to be coordinated as a team to win a championship. In healthcare, a patient is better served with a well-trained primary physician to coordinate with the various medical specialists. The field of semiconductors involves a series… Read More

RISC-V processor IP is abundant. Open-source code for RISC-V is also widely available, but typically project-based code solves one specific problem. Using only pieces of code, it’s often up to a development team integrate a complete application-ready stack for creating an embedded device. A commercial embedded software development… Read More

Advanced Packaging Analysis at DesignConby Tom Dillinger on 06-07-2022 at 10:00 amCategories: EDA, Xpeedic

The slogan for the DesignCon conference has been “where the chip meets the board”. Traditionally, the conference has provided a breadth of technical presentations covering the design and analysis of high-speed communication interfaces and power integrity evaluations between chip, board, and system.

The recent DesignCon… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center