Dan is joined by Kevin Robinson, yieldHUB’s Vice President of Operations who was recently appointed Head of Sales for Europe, the Middle East & Africa. With over 23 years of experience as a test engineer in the semiconductor industry, Kevin brings a wealth of knowledge and dedication to his dual role. At yieldHUB, Kevin leads… Read More

Bram co-founded ICsense in 2004 as a spin-off of the University of Leuven. He is CEO since 2004 and helped growing the company from 4 to over 100 people in 20 years while being profitable every year. He managed the acquisition by TDK in 2017. He is an experienced entrepreneur in the micro-electronics field with a strong interest in … Read More

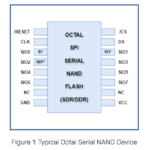

As the automotive industry continues to evolve, the demands for high-capacity, high-speed storage solutions are intensifying. Autonomous vehicles and V2X (Vehicle-to-Everything) communication systems generate and process massive amounts of data, necessitating advanced storage technologies capable of meeting these… Read More

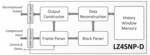

Data compression is a critical element of many systems. Thanks to trends such as AI and highly connected systems there is more data to be stored and processed every day. Data growth is staggering. Statista recently estimated that 90% of the world’s data was generated in the last two years. Storing and processing all that … Read More

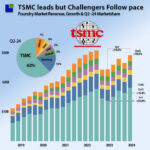

The global semiconductor market reached $149.9 billion in the second quarter of 2024, according to WSTS. 2Q 2024 was up 6.5% from 1Q 2024 and up 18.3% from a year ago. WSTS revised 1Q 2024 up by $3 billion, making 1Q 2024 up 17.8% from a year ago instead of the previous 15.3%.

The major semiconductor companies posted generally strong… Read More

Similar to analog circuits, which use EM waves at communications frequencies, components in photonics integrated circuits (PICs), which use EM waves at optical frequencies, are sensitive to layout and manufacturing variations—arguably more so. Similar to their semiconductor counterparts, which transmit information… Read More

Dan is joined by Jim Handy of Objective Analysis. Jim is a 35-year semiconductor industry executive and like Dan, a leading industry analyst, speaker, and blogger. Following marketing and design positions at Intel, National Semiconductor, and Infineon, Jim became highly respected as an analyst for his technical depth, accurate… Read More

Now that live events are filling up there are even more live events especially here in Silicon Valley. Synopsys, the #1 full IP provider, will host a processor summit here in Santa Clara next month. Given the popularity of anything RISC-V, I would expect this event to be very well attended so be sure and register in advance.

The networking… Read More

If you work in the Semiconductor or related industry, you know that industry cycles can profoundly impact your business. It is crucial for strategic development to invest at the appropriate time and to rope the sails when necessary.

As a semiconductor investor, you’re accustomed to the ebb and flow of industry cycles. It’s… Read More

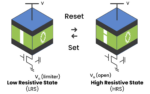

It’s well known that flash is the embedded non-volatile memory (NVM) incumbent technology. As with many technologies, flash is bumping into limits such as power consumption, speed, endurance and cost. It is also not scalable below 28nm. This presents problems for applications such as AI inference engines that require embedded… Read More

![IMG 0411[6]](https://semiwiki.com/wp-content/uploads/2024/08/IMG_04116-150x100.jpg)

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center