At DAC I talked with Mike Dimelow of ARM about the latest upcoming revision to the AMBA bus standards, AMBA 4. The standard gets an upgrade about every 5 years. The original ARM in 1992 ran at 10MIPS with a 20MHz clock. The first AMBA bus was a standard way to link the processor to memories (through the ARM system bus ASB) and to peripherals… Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read MoreDesign for test at RTL

Design for test (DFT) imposes various restrictions on the design so that the test automation tools (automatic test pattern approaches such as scan, as well as built-in self-test approaches) will subsequently be able to generate the test program. For example, different test approaches impose constraints on clock generation… Read More

Intel Twisting ARM?

Intel’s new Tri-Gate technology is causing quite a stir on the stock chat groups. Some have even said if Intel uses its Tri-Gate technology on only Intel processors ARM will be in deep deep trouble. These guys are “Intel Longs” of course and they are battling “Intel Shorts” with cut and paste news clips.

“ARM is in trouble & this… Read More

Low Power Webinar Series

At DAC 2011 in San Diego, Apache gave many product presentations. Of course not everyone could make DAC or could make all the presentations in which they were interested. So from mid-July until mid-August these presentations will be given as webinars. Details, and links for registration, are here on the Apache website.

The seminars… Read More

Once Upon A Time… ASIC designers developed IC for Supercomputer in the 80’s

During last week-end, I had the good surprise to meet with one of my oldest friend, Eric, who remind me the old time, when we were working together as ASIC designers for… a Supercomputer project.

In France, in a French company (Thomson CSF) active in the military segment and being able to spend which was at that time a fortune ($25M) … Read More

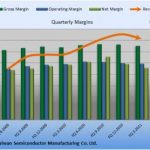

TSMC Financial Status Plus OIP Update!

Interesting notes from my most recent Taiwan trip: Taiwan unemployment is at a record low. Scooters once again fill the streets of Hsinchu! TSMC will be passing out record bonuses to a record amount of people. TSMC Fab expansions are ahead of schedule. The new Fab 15 in Taichung went up amazingly fast with equipment moving in later… Read More

Two More Transistor-Level Companies at DAC

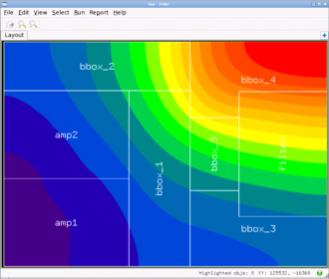

In my rush on Wednesday at DAC I had almost over-looked the last two companies I talked with: Invarian and AnaGlobe. These last two I had hand-written notes on paper, so I just got to the bottom of my inbox tonight to write up the final trip reports.

Invarian

Jens Andersen and Vladimir Schellbach gave me an overview of tools that perform… Read More

Apache Design Automation acquired by Ansys

We all knew that Apache had filed for an IPO earlier and were just waiting for the timing and price to be revealed. Rumors have been circulating about an acquisition and today we know that the rumors were true asAnsys paid $310 million in cash for Apache.

Ansys stock has surged some 35% over the past twelve months:

Products

This acquisition… Read More

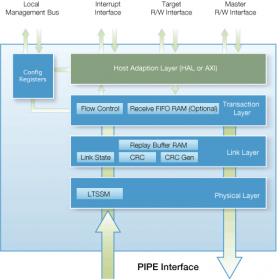

Cadence to launch PCIe gen-3 (8 GT/s) IP and VIP: fruit of Denali acquisition

The recent announcement from Cadence, officially launching the PCI Express 3.0 Controller IP, as well as the associated Verification IP (VIP), made of Compliance Management System (CMS) which provides interactive, graphical analysis of coverage results, and PureSuite which provides the PCIe associated test cases, clearly… Read More

SOC Realization

There are some very interesting comments to the last entry on SoC Realization and how more and more chips are actually assembled out of IP. There was clearly a lot of discussion in this area at DAC, although most people (Atrenta being an exception) don’t use the term SoC Realization, presumably because it was originated by … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era