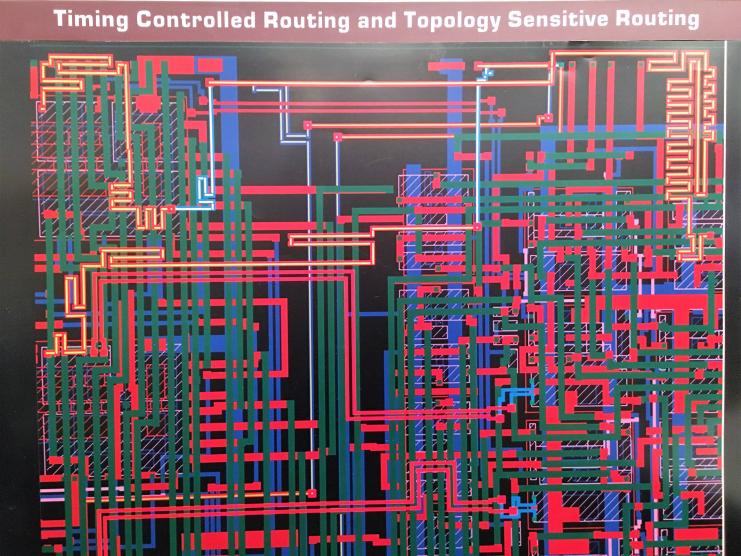

The year is now 1991 and in search for a more peaceful life we decided to move to Canada. At that time, very few companies had advanced flows in VLSI but Ottawa having BNR, Northern Telecom, Mitel, etc., looked to be the most promising place. After a few hiccups in finding a job, I landed in MOSAID, a small company with35 people at that … Read More

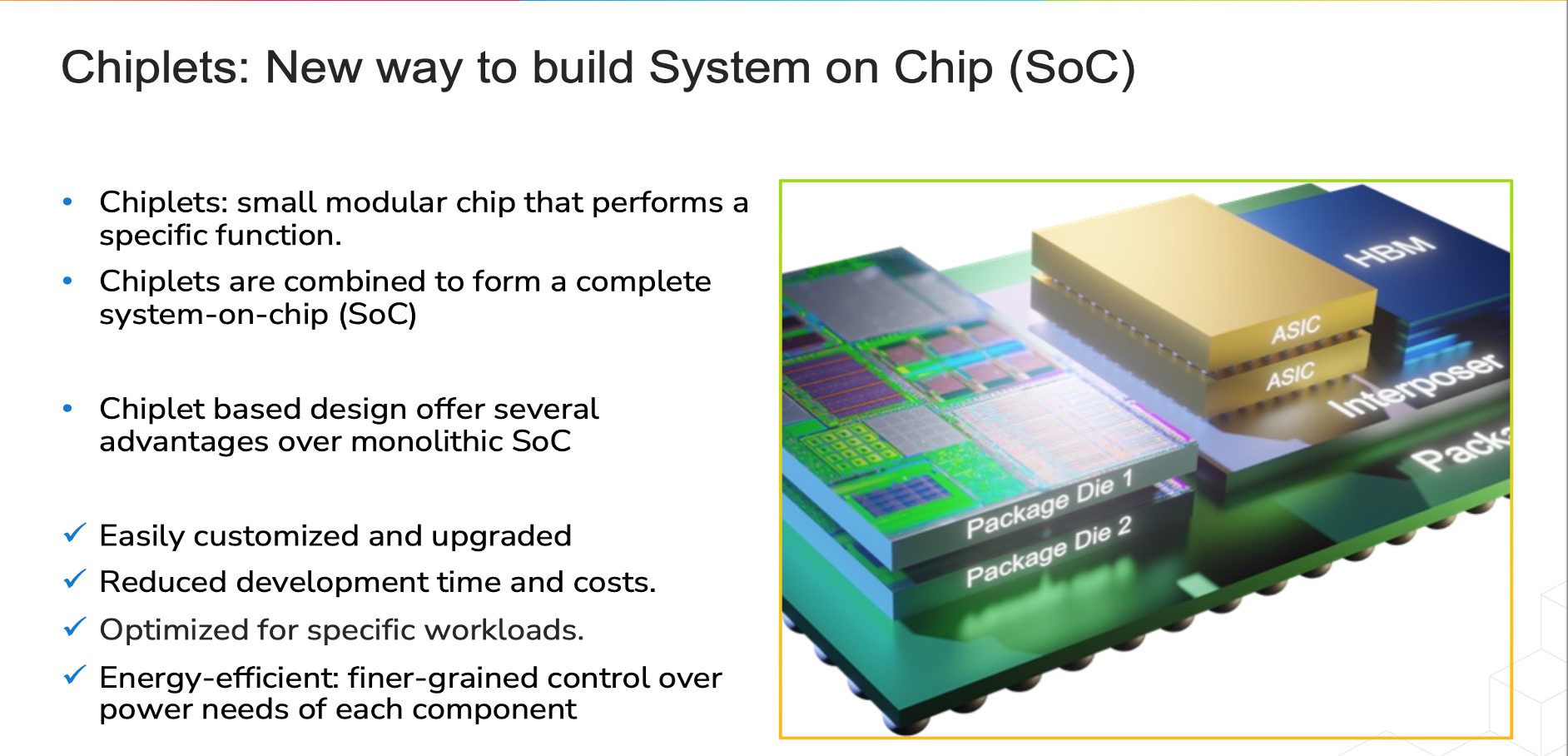

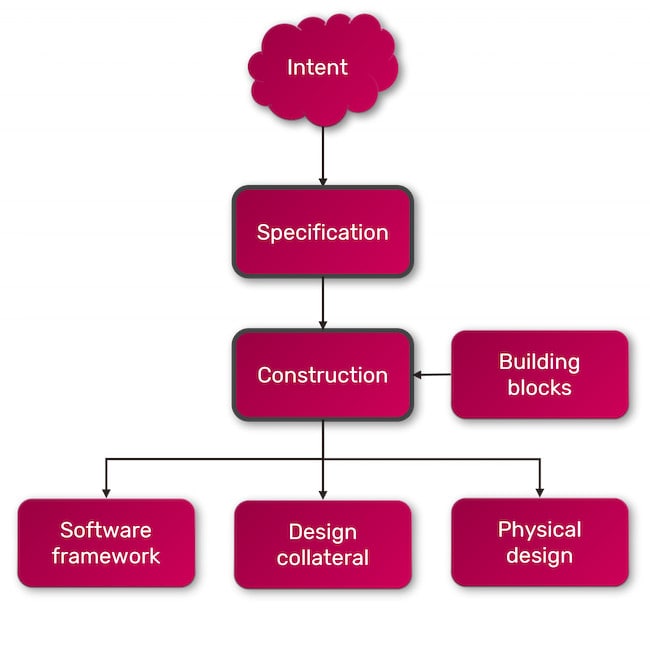

Streamlining Functional Verification for Multi-Die and Chiplet DesignsAs multi-die and chiplet-based system designs become more…Read More

Streamlining Functional Verification for Multi-Die and Chiplet DesignsAs multi-die and chiplet-based system designs become more…Read More S2C Advances RISC-V Ecosystem, Accelerating Innovation at 2025 Summit ChinaShanghai, July 19, 2025 — S2C, a leader in functional…Read More

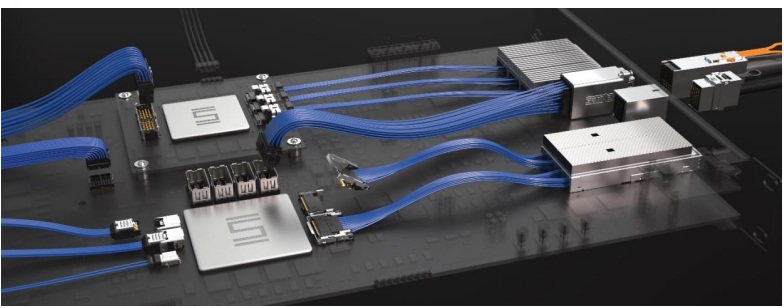

S2C Advances RISC-V Ecosystem, Accelerating Innovation at 2025 Summit ChinaShanghai, July 19, 2025 — S2C, a leader in functional…Read More Samtec Practical Cable Management for High-Data-Rate SystemsAccording to a recent Samtec whitepaper, in high-data-rate…Read More

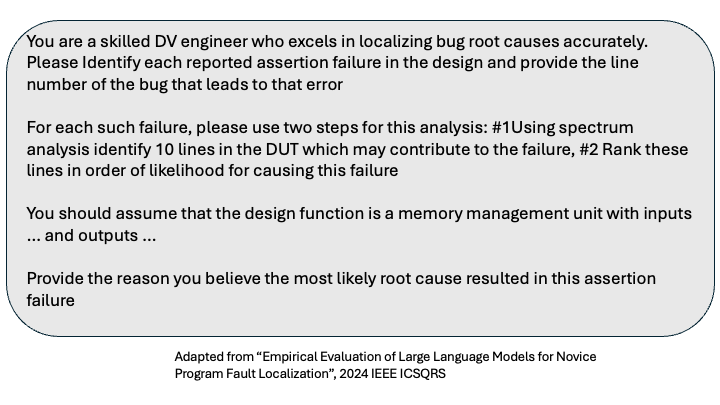

Samtec Practical Cable Management for High-Data-Rate SystemsAccording to a recent Samtec whitepaper, in high-data-rate…Read More A Quick Tour Through Prompt Engineering as it Might Apply to DebugThe immediate appeal of large language models (LLMs)…Read More

A Quick Tour Through Prompt Engineering as it Might Apply to DebugThe immediate appeal of large language models (LLMs)…Read MoreNetworking and Formal Verification

I attended Oski’s latest Decoding Formal event a couple of weeks ago and again enjoyed a largely customer-centric view of the problems to which they apply formal, and their experiences in making it work for them (with Oski help of course). From an admittedly limited sample of two of these events, I find them very representative of… Read More

IoT Project Planning – Profiting from the Folly of Others

I recently was introduced to a white paper written by John Stabenow, Director at Mentor, a Siemens Business, that gave an excellent overview of things to consider before launching into the design of an IoT edge project. John starts the paper with a quote from Pliny the Elder (A.D.23-A.D.79) who said, “The best plan is, as the common… Read More

CES Preview with Cadence!

The Consumer Electronics Show (CES) is in its 50th year believe it or not! The first one was in New York (1967) with 250 exhibitors and 17,500 attendees. Portable radios and TVs were all the rage followed by VCRs in 1970 and camcorders and compact discs in 1981. This year there will be 3,900+ exhibits and an estimated 170,000 attendees… Read More

Self-Monitoring SoCs – An Idea Coming of Age

In a former life I was the GM of a business where we built specialized structures used for semiconductor process bring-up, characterization and monitoring. These monitoring structures were placed in wafer scribe-lines and were used to monitor key parameters during wafer processing. The structures provided feedback to automated… Read More

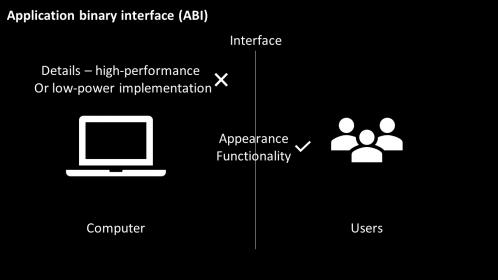

Application binary interface, get this right and RISC-V is all yours

Starting a career in static timing analysis domain, and now actively working on an opensource implementation flow of RISC-V architecture, has been a journey. For last couple of months, I guess from around March this year, I was hooked to RISC-V buzz which was all over my Linkedin, my messages.

Being an STA and Physical design engineer,… Read More

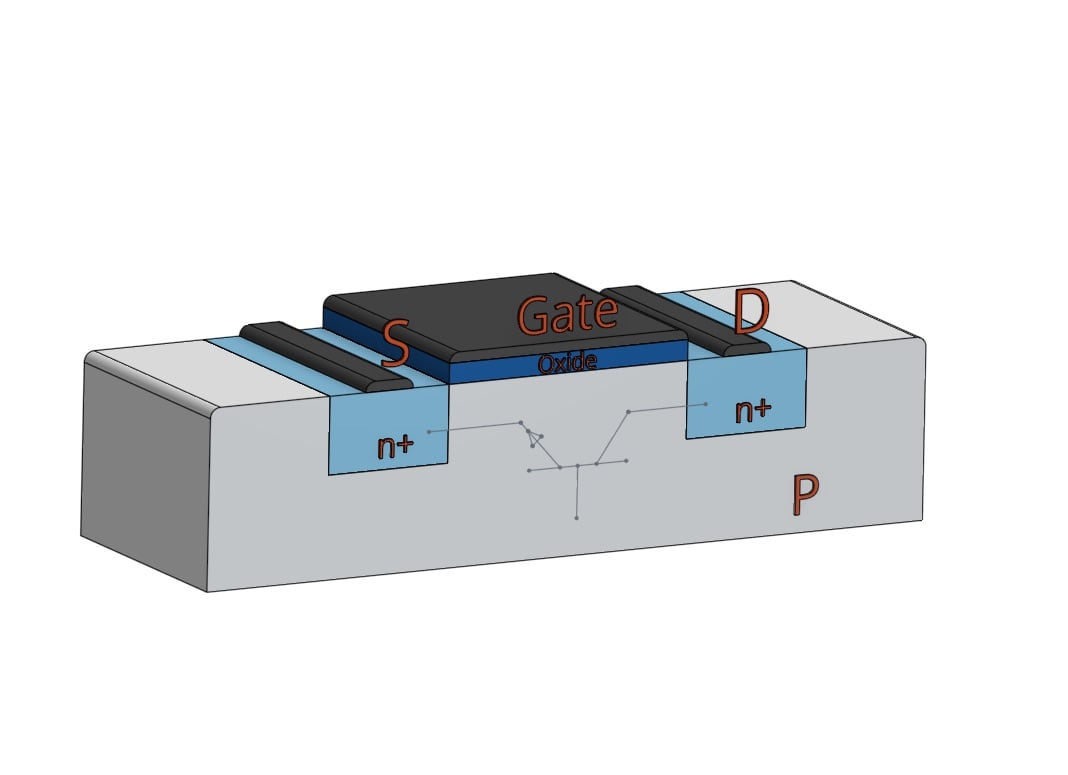

Snapback behavior determines ESD protection effectiveness

Terms like avalanche breakdown and impact ionization sound like they come from the world of science fiction. They do indeed come from a high stakes world, but one that plays out over and over again here and now, on a microscopic scale in semiconductor devices – namely as part of electrostatic discharge (ESD) protection. Semiconductor… Read More

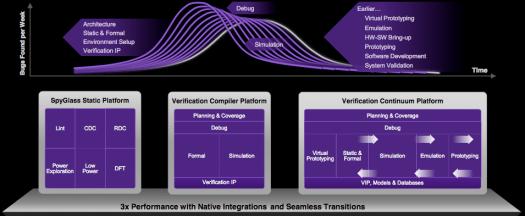

Shifting Left with Static and Formal Verification

Unless you have been living in a cave for the last several years, by now you know that “Shift Left” is a big priority in product design and delivery, and particularly in verification. Within the semiconductor industry I believe Intel coined this term as early as 2002, though it seems now to be popular throughout all forms of technology… Read More

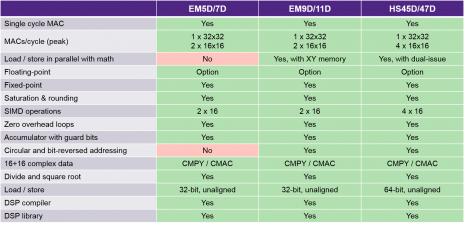

DSP Benchmarks and Libraries for ARC DSP families

Synopsys DesignWareARC HS4xD family is a perfect example of high performance DSP, enhanced RISC CPU IP core, able to address high-end IoT, mid to high-end audio or baseband control. ARC HS4xD architecture is 10-stage pipeline for high Fmax, resulting in excellent RISC efficiency with 5.2 CoreMark per MHz. ARC EMxD processors… Read More

Webinar: ADAS and Real-Time Vision Processing

ADAS is in many ways the epicenter of directions in the driverless car (or bus or truck). Short of actually running the car hands-free through a whole trip, ADAS has now advanced beyond mere warnings to providing some level of steering and braking control (in both cases for collision avoidance), providing more adaptive cruise control,… Read More

Should the US Government Invest in Intel?