In a DRAM chip, the memory array contains features which are the most densely packed, but at least they are regularly arranged. Outside the array, the regularity is lost, but in the most difficult cases, the pitches can still be comparable with those within the array, though generally larger. Such features include the lowest metal lines in the periphery for the sense amplifier (SA) and sub-wordline driver (SWD) circuits.

A key challenge is that these lines are meandering in appearance, and the pitch is varying over a range; the local max/min pitch ratio can range from ~1.4 to 2. These pitches have different focus windows [1], and in EUV lithography, these windows may be separated by more than the resist thickness [2].

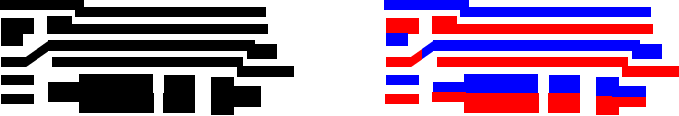

Pitch uniformity within a single exposure can be attained if the layout is split accordingly for double patterning with stitching [3,4] (Figure 1). The layout is dissected into stripes of alternating color, each color assigned to one of two exposures. Features may cross stripe boundaries; in that case, the two exposures need to stitch correctly at the boundaries.

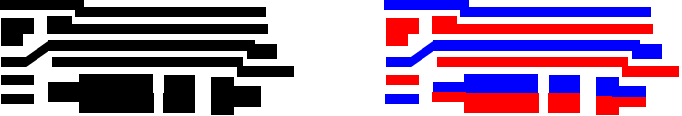

Alternatively, some features like diagonals may be forbidden to be stitched, resulting in a different layout split (Figure 2).

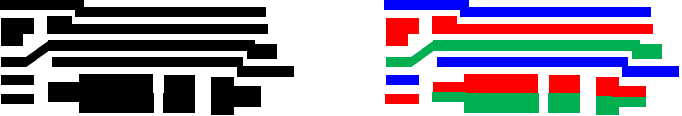

For minimum pitches above 40 nm, we expect double patterning to be sufficient with ArF immersion lithography. In case the minimum pitch is lower than this, triple patterning may be used (Figure 3) with ArF immersion lithography, as an alternative to EUV double patterning.

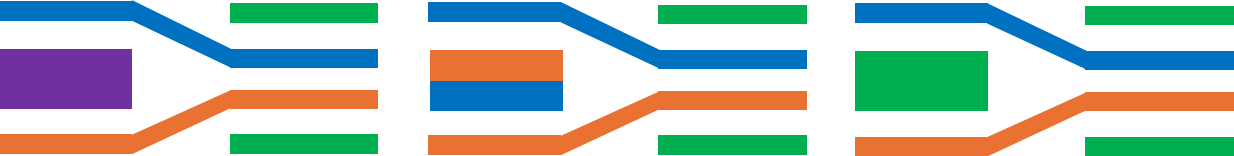

Previously, quadruple patterning was suggested for where the minimum line pitch is less than 40 nm [1], but it turns out triple patterning may suffice (Figure 4).

References

[1] F. Chen, Application-Specific Lithography: Sense Amplifier and Sub-Wordline Driver Metal Patterning in DRAM.

[2] A. Erdmann et al., J. Micro/Nanolith. MEMS MOEMS 15, 021205 (2016); E. van Setten et al., 2012 International Symposium on EUV Lithography.

[3] Y. Kohira et al., Proc. SPIE 9053, 90530T (2014).

[4] S-Min Kim et al., Proc. SPIE 6520, 65200H (2007).

[5] F. Chen, Triple Spacer Patterning for DRAM Periphery Metal.

[6] C-M. Lim, Proc. SPIE 11854, 118540W (2021).

Thanks for reading Multiple Patterns! Subscribe for free to receive new posts and support my work. Pledge your support.

Also Read:

A Perfect Storm for EUV Lithography

Variable Cell Height Track Pitch Scaling Beyond Lithography

A Realistic Electron Blur Function Shape for EUV Resist Modeling

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center