…but what is the weight of the Verification IP market?

If the IP market is a niche market (see: **) with revenue of about 1% of the overall semiconductor business, how could we qualify the VIP market? Ultra-niche market? But the verification of the IP integrated into the SoC is an essential piece of the engineering puzzle when you are involved in SoC design. Let me clarify what type of verification I want to discuss: the verification of a protocol based function, which can be an Interface protocol (USB, PCIe, SATA, MIPI and more), a specific memory Interface (DDR, DDR2,…, GDDR,…, Flash ONFI and more) or a Bus protocol (AMBA AXI,…, OCP and more).

** http://www.semiwiki.com/forum/f152/ip-paradox-such-low-payback-such-useful-piece-design-369.html

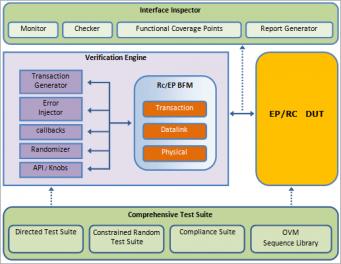

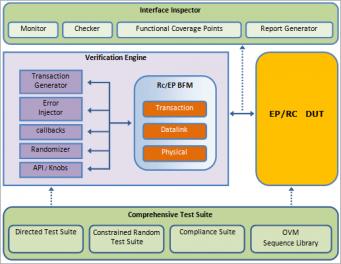

Courtesy of Perfectus

The principle of this type of VIP is: you write Test benches, send to a scenario Generator which activates the Drivers of the Bus Function Model (BFM), accessing the function you want to verify, the Device Under Test (DUT). The Verification Engine itself is made of the transaction Generator, Error injector and so on and of the BFM, which is specific to the protocol and to the agent configuration: if the DUT is a PCIe Root Port x4, the BFM will be a PCIe End Point x4. If the DUT is the hand, the BFM is the glove. When you write Test benches, you in fact access to a library of protocol specific test suite (test vectors written by the VIP vendor), which is sold on top of the VIP. So, after applying test benches, you have now to monitor the behavior of the DUT and check for the compliance with the protocol specification. This defines another product sold by the VIP vendor: the Monitor/Checker, which allows you to evaluate both the coverage of your Test Benches, and the compliance in respect with the protocol.

Common sense remark about the BFM and IP: when you select a VIP provider to verify an external IP, it is better to make sure that the design team for the BFM and for the IP are different and independent (high level specification and architecture made by two different person). This is to avoid the “common mode failure”, principle well known in aeronautic for example.

If we look at this products from a cost perspective, the unit cost is relatively low (in the few $10K), but as you probably know, the verification task weight is heavy (60 or 70% of the overall design project), so you want to parallelize as much as possible to minimize the time devoted to verification. To do so, you have to buy several licenses for the same VIP, ending up to a cost being in the few $100K per project. Now, if we try to evaluate the market size of the VIP, like we can do for the Design IP, we realize that there is no market data available. We simply don’t know it! Making an evaluation is absolutely not straightforward. You could think that looking at the number of IP licenses sold for protocol based function (above listed) could lead to a simple equation: Market Size = (Nb of IP Licenses) x (average cost of VIP).

But that does not work! In fact, the people buying an IP do not necessarily run the complete Verification on it, but some IDM or Fabless do it: it is not a binary behavior! That you can say is that a design team who internally develop a protocol based function will most certainly run a complete Verification of the function. But you don’t know precisely how many IDM or Fabless prefer developing internally a protocol based function rather than buying an IP!

If we look at the VIP players, we see that Cadence has heavily invested into this market: when they bought Denali in 2010 (for $315M), they bought a strong VIP port folio and competencies, and probably good market share. They also bought products from Yogitech SpA, IntelliProp Inc. and HDL Design House in October 2008 to complete their port-folio. When you consider that Synopsys integrates their VIP into Design Ware, so they do not try to get value for each VIP, you can say that there is a kind of Yalta: Design IP to Synopsys, VIP to Cadence. But Cadence is not alone, and face pretty dynamic competition, mostly coming from mid size companies with R&D based in India and sales offices in the US (VIP is design resources intensive), like nSys, Perfectus, Avery, Sibridge Technologies and more.

The VIP paradox: we don’t know the market size, but VIP is an essential piece of the puzzle for SoC design, as most of the SoC are using several protocols based functions (sometimes up to several dozen). We don’t know if just selling VIP is a profitable business, or if you need to also provide design services (like many vendors do). That we propose is to run a market survey, asking to the VIP vendors to disclose their revenue, so we could build a more precise picture of this market, evaluating the current size, understand the market trends and building a forecast. The ball is in the VIP vendor camp!

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center