I had lunch today with a guy who has to remain nameless. But he is on the edge of the semiconductor lithography thing. He told me EUV will never happen. Of course lots of people have said that. Me for one. But he said everyone knows it. The investment community, the foundries, everyone. Intel put money into ASML in the hopes that it would work. TSMC added a little more and a week later the schedule slipped out by a year or so.

I had lunch today with a guy who has to remain nameless. But he is on the edge of the semiconductor lithography thing. He told me EUV will never happen. Of course lots of people have said that. Me for one. But he said everyone knows it. The investment community, the foundries, everyone. Intel put money into ASML in the hopes that it would work. TSMC added a little more and a week later the schedule slipped out by a year or so.

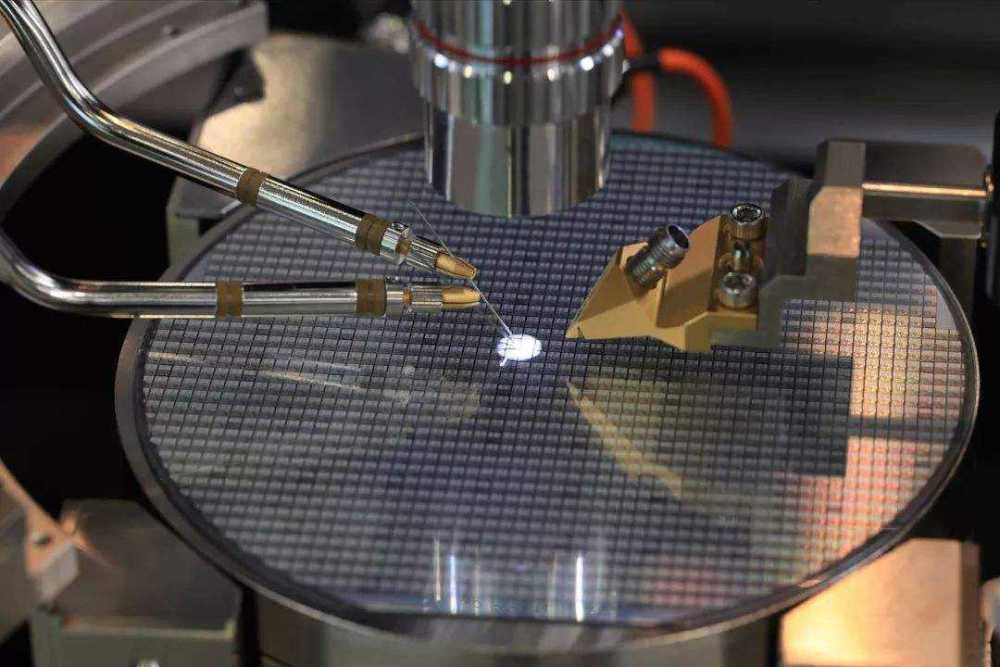

The big problem is the light source. You may or may not know that it is like something out of a science fiction movie. Droplets of liquid tin fall. One laser hits it to shape the drop; then another really big one really zaps it and a few percent of the lasers energy is dissipated as EUV radiation at 13.5nm. Which is absorbed by everything, so everything has to be in a vacuum. And masks have to reflective, not refractive (mirrors not lenses). Then a lot of mirrors shape the beam before directing it onto the “mask” which is actually a mirror. And all the mirrors are not like in your bathroom. They would absorb EUV too. They are silicon/molybdenum layers that reflect by interference. So only about 30% gets reflected. Two problems. There is not much light getting through and the mirrors are getting hot.

So the EUV light sources are nowhere near powerful enough and the photoresists are not sensitive enough. The laser is maybe 10% efficient (so a 100MW laser requires 1GW of power in he subfloor under the fab) and the optical path lets 3% of the light hit the wafer. But each year of delay has a new problem. The numerical apterture (NA, google it if you don’t know what it means) is constantly getting worse. So you need a couple more mirrors in the optical path. Oops. 50% less light gets to the wafer (remember the mirrors are not very efficient).

The problem I think is totally underrated is the pellicle issue. In normal semiconductor manufacturing (193nm immersion lithography) the mask has a protective layer to keep contamination out of the focal plane so it won’t print even if it happens. But everything absorbs EUV so no pellicle on the “mask” which is a mirror. So every little thing will get on the mirror and print. For wafer after wafer. Until the mask is cleaned. Which is a new problem, since you cannot clean the mask forever without damaging the pattern. And you have a vacuum with dripping molten tin and stuff. Not a contamination free zone.

So EUV is not going to happen.

My other discussion with my nameless friend was 450mm. Not going to happen either. There is just no economic justification for it. If EUV doesn’t happen (see above) then a lot of the cost of the fab is tied up in double, triple, quadruple patterning. But that is tied to the area of the wafer, not the number of wafers, so 450mm and 300mm cost roughly the same per die. A stepper exposes one die at a time. So a minor saving on wafer changes but none on exposures. Plus at the edge of the huge wafers nobody has got it to work yet. They don’t yield.

So the two big “get out of jail free” cards for the semiconductor industry won’t happen. We are stuck with 193nm lithography, multiple patterning, 300mm wafers. And a handful of state of the art fabs.

Share this post via:

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?