The complexity of silicon chips is exploding. Actually, it has been growing at a tremendous speed for decades. So far, the semiconductor industry has been successful at providing new ways to master new levels of complexity, over and over again.

The complexity of silicon chips is exploding. Actually, it has been growing at a tremendous speed for decades. So far, the semiconductor industry has been successful at providing new ways to master new levels of complexity, over and over again.

Standardizing hardware platforms, using higher-level languages with a knowledge of the underlying hardware (like OpenCL), heavily reusing IPs, simulating from system to the gate, speeding up our EDA software, leaving the bulk of functionality to software…

All this has been a relentless quest for new strategies to master complexity.

We all know that this is not always a rosy picture, however. Despite adopting new strategies and deploying new tools, making an ASIC, a SoC or a FPGA ready for production is a long path paved with sweat, doubts and excitement too.

How about ‘Desillusion’? Maybe as well.

We,FPGA engineers, have run against quite some of it. For some time, we had thought that we had been blessed among other electronic engineers, because, well, the chip can be changed and fixed in the field, right?No worries about the high NRE cost, no risk of wasting a few 100th of millions dollars because of a respin.

Using a prototype provides much faster execution than simulation and reveals the imperfections of the models we use in simulation.

In the end, we can just take a sample in the field before production, so there is no risk of any unforeseen behavior…

Right? Right?

Well, not quite. Prototyping a complex chip on a FPGA is a good approach only if you can get a reasonable visibility out of it. Once on a board, a chip is fast and essentially opaque.

Should we give up debugging and analysis on FPGA prototypes because we lack visibility? Actually, using FPGA prototypes is not the problem. The problem is that the tools we use with FPGA prototypes did not scale with their gigantic complexity. Using FPGA prototypes is not the problem. The problem is that the tools we use did not scale with FPGAs’ gigantic complexity.

‘Did not’ scale you say?

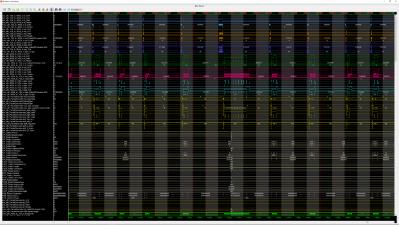

Please watch the recording below: it show a capture of live data from inside a FPGA placed in the field, that spans over more than 1 hour – that is far more than what simulation usually shows – and this, in real condition.

For more information, you can contact meor go to : www.exostivlabs.com

Thank you for reading –

-Frederic Leens

Exostiv Labs provides innovative solution to debug FPGA. Our software / hardware products provide up to 100.000 times more observability than the usual embedded instrumentation solutions at the FPGA speed of operation. Today’s FPGA complexities require a new generation of debugging tools. Exostiv Labs focuses on reaching ultra large observability while preserving the target FPGA memory and I/O resources. This allows visiting new debugging scenarios, with extended reach in time and unprecedented Gigabyte-range debug information recordings.

Share this post via:

Solving the EDA tool fragmentation crisis