One of the privilages of blogging for SemiWiki is invitations to the top conferences around the world including the International Solid-State Circuits Conference (ISSCC) in San Francisco this week. Amazing, this conference is older than I am:

ISSCC 2013 is the 60th Conference in an incredibly long-lasting series. Following the invention of the transistor in 1947, there was a developing interest in transistor circuit design. This coalesced in 1954, with the creation of the first “Conference on Transistor Circuits”, held in Philadelphia, sponsored by the IRE, one of the predecessors of the IEEE. Since then, transistor-circuit design which evolved into integrated-circuit design has changed the world like no other technology ever has. Propelled by this sixty-year history, ISSCC 2013 will provide a special opportunity for looking back to the future, toward further exciting developments in solid-state circuits and systems. ISSCC remains the premier forum in the world where circuit innovations are presented. In this role, ISSCC will continue to (em)power the future!

The advanced program is HERE, if you want to avoid me do NOT attend these sessions:

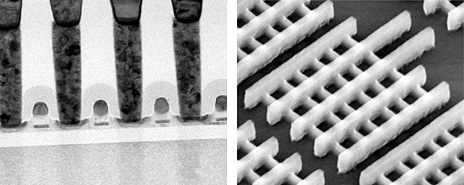

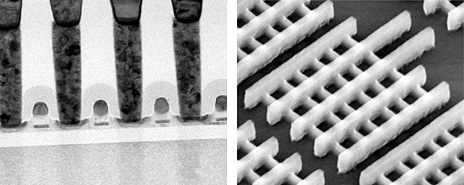

T4: Circuit Design using FinFETs

After HKMG, FinFETs are a powerful yet disruptive technology to enable continuous scalingfollowing Moore’s law. The disruptive nature arises from both the 3D structure and the quantization on width choice. FinFETs require new design skills to trade-off among PPA (powerperformance-area) and to conduct circuit-process co-optimization. Salient advantages ofFinFETs include: increased driving capability per footprint area, better control on short-channeleffect, subthreshold slope, and less requirement on channel doping. Thus, threshold voltagecan be reduced, which enables a reduction in supply voltage and thus power consumption or increase of performance speed.

The tutorial will focus on critical issues of FinFET design: It starts with a crisp comparison ofplanar vs. 3D FinFET devices and the associated SPICE modeling. Next, logic design is presented,including effects on standard cells, I/O circuitry, and ESD. Then, the subjects of SRAMand analog/mixed-signal design are treated in detail. Digital chip-level design that requiresmethodology enhancement and new CAD tool features are carefully discussed. The tutorialwill enable CMOS designers to systematically comprehend circuit design using FinFETs.

As I have mentioned before, FinFETs will be the most significant piece of technology we, as semiconductor ecosystem people, will experience this decade. Attend every FinFET seminar, read every FinFET paper, stay glued to SemiWiki because FinFETS will set the semiconductor ecosystem on fire. FinFETs will keep the mobile world powered up, FinFETs will set the foundries apart. It’s coming, believe it.

ES3: High-Speed Communications on 4 Wheels: What’s in your Next Car?

Communications inside vehicles is experiencing a growing demand due to applications likeinfotainment, driver assistance, safety systems and diagnostics, requiring data-rates beyondwhat is offered by current solutions.

Considering that cabling is the third highest cost factor and the third heaviest component inthe car, there is a clear need to go beyond the current low data-rate solutions and convergeto a high data-rate backbone network. Solutions, both electrical and optical, are being proposed by car-makers and silicon manufacturers. The evening session will give an overviewon the status and outlook on an emerging market that is already shipping 650 million communication ports per year.

One of the biggest disappointments at CES this year was the cars of the “future”, we can do better.

EP3: Empowering the Killer SoC Applications of 2020

A distinguished panel from global industry and academia will debate the nature of systemsdriving the killer applications of 2020. Can we forecast the future killer applications? We havehad the computing revolution, then communications, and now the sensor era. Are sensorsdriving the next killer applications? Are there any other revolutions in sight? What circuitsand system innovations can ISSCC bring forward for the next killer applications? What technology elements, device structures and memory architectures are required? Should we continue with silicon technology and find breakthroughs through system architecture, algorithms, SoC integration and packaging? Or should we prepare for “beyond silicon” technologies? Are any beyond-silicon technologies realistic for the future?

For those of you who don’t know, Fisherman’s Wharf has great seafood and is a Cable car ride away. Scoma’s is my favorite but just eating a bowl of cioppino on the waterfront is fine too. The weather looks good but bring an umbrella because it is San Francisco and you just never know. I have an ISSCC umbrella from last year somewhere.

For those of you who don’t know, Fisherman’s Wharf has great seafood and is a Cable car ride away. Scoma’s is my favorite but just eating a bowl of cioppino on the waterfront is fine too. The weather looks good but bring an umbrella because it is San Francisco and you just never know. I have an ISSCC umbrella from last year somewhere.

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center