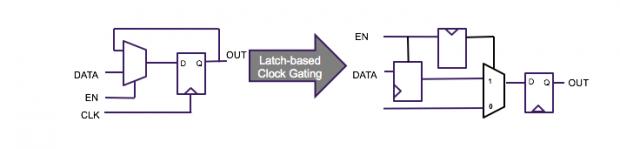

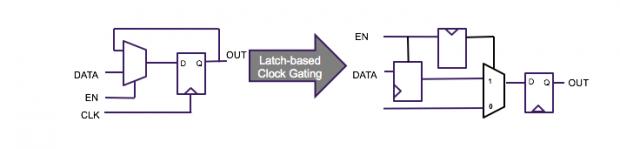

Clock gating is arguably the mostly widely-used design method to reduce power since it is broadly applicable even when more sophisticated methods like power islands are ruled out. But this style can be fraught with hazards even for careful designers. When you start with a proven-correct logic design and add clock gating, the logic (and timing) can change in ways which are not an intuitively simple extension of the original design, raising the need to validate that those changes have not broken the logic intent.

REGISTER HERE for Webinar on July 11[SUP]th[/SUP] at 10am PDT

The problem sounds similar to validating that synthesized logic is functionally equivalent to original RTL and we know how to deal with that problem – run logic equivalence checking between the RTL and the synthesized netlist. But that doesn’t work for clock gating checks because conventional equivalence checking (mostly) checks combinationallogic equivalence between reference points. However, clock gating structures are inherently sequential; traditional equivalence engines don’t work with this kind of problem – you need to use sequential equivalence checking (SEQ), still a formal-based check but allowing for cycle-shifted equivalence.

Why not simply use dynamic verification to verify the correctness of this gating? You could but (a) you have to extend your testbenches to add directed tests for clock-gating, not only increasing the complexity of testing but also dramatically increasing verification run-times and (b) you have to consider all possible variations of switching versus functionality in each case. Or you could verify formally, which doesn’t impact your dynamic verification setup or run-times at all and is intrinsically complete. And, by the way, VC Formal SEQ is an app, so much easier to use than traditional formal. Hmm – which way to go? Maybe you should check out the webinar.

REGISTER FOR THIS WEBINAR to learn how you can use VC Formal to formally verify the sequential equivalence of a clock gated circuit with the original logic, to have full confidence that your logic intent has been preserved.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.