When I worked at Intel designing custom chips my management would often ask me, “Will first silicon work?” My typical response was, “Yes, but only for the functions that we could afford to simulate before tape-out.” This snarky response would always cause a look of alarm, quickly followed by a second look of disbelief, and so it goes on in a similar vein today. You can design an IC and get first silicon working well enough to begin selling it, however the big challenge is how to find all of those functional bugs and fix them before tape-out happens.

On Tuesday night I went out for my weekly group ride with other road bike enthusiasts here in Tualatin, however my Garmin 520 bike computer showed only a 2% charge, so I quickly opted for plan B which was to use my Android phone and the Strava app instead. I started up the app, clicked the big Green Go button. I then clicked the power button lightly and the screen shut down to save power, then I did my bike ride. At the end of the ride, I clicked the power button and pushed the Red Stop button. To my horror the app didn’t save the GPS route of my ride at all, something glitched in the app while the screen was powered down. I cannot say that it was the fault of the Android phone, or just the app, but it illustrates what can happen when a complex device like a smart phone tries to conserve power by having multiple power-saving modes.

Garmin 520 – please make the battery last longer

Strava app – please make it work reliably when the phone goes into power savings mode

To help you avoid a field failure like mine, you would want to view an archived webinar from Synopsys called:

Related blog – Catching low-power simulation bugs earlier and faster

The three main ideas in this second webinar of the series are:

[LIST=1]

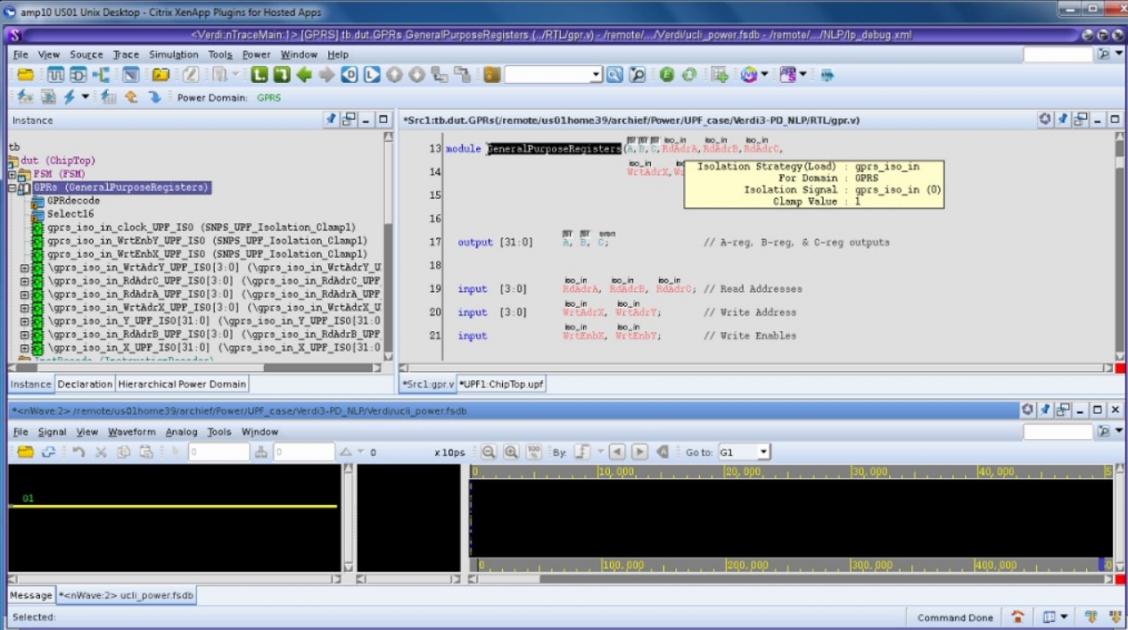

Synopsys has two people in this webinar, Vaishnav Gorur and Archie Feng, and they go over the methodology of using a power architecture defined in UPF while the design is specified with an RTL description. Verifying that your power architecture is implemented properly is a big challenge because of how complex power reduction schemes have become, which enable longer lasting battery-powered devices like the Garmin cycling computers and popular smart phones.

Using Verdi to debug an SoC

Comments

0 Replies to “Power-Aware Debug to Find Low-Power Simulation Bugs”

You must register or log in to view/post comments.