Synopsys is bridging its long-running ARC® processor IP strategy into a RISC-V architecture – Bernard Murphy introduced the news here on SemiWiki last November. We’re getting new insight from Synopsys on its ARC-V™ portfolio and how they see RISC-V IP plus their mature software development toolchain IP fitting customer needs in automotive, consumer, IoT, networking, storage, and other applications. The portfolio, unveiled at a RISC-V Summit Silicon Valley keynote in November, shows Synopsys scaling the RISC-V ISA smoothly across three tiers of 32- and 64-bit host-based, real-time, and embedded processing needs.

Bringing more RISC-V resources for developers

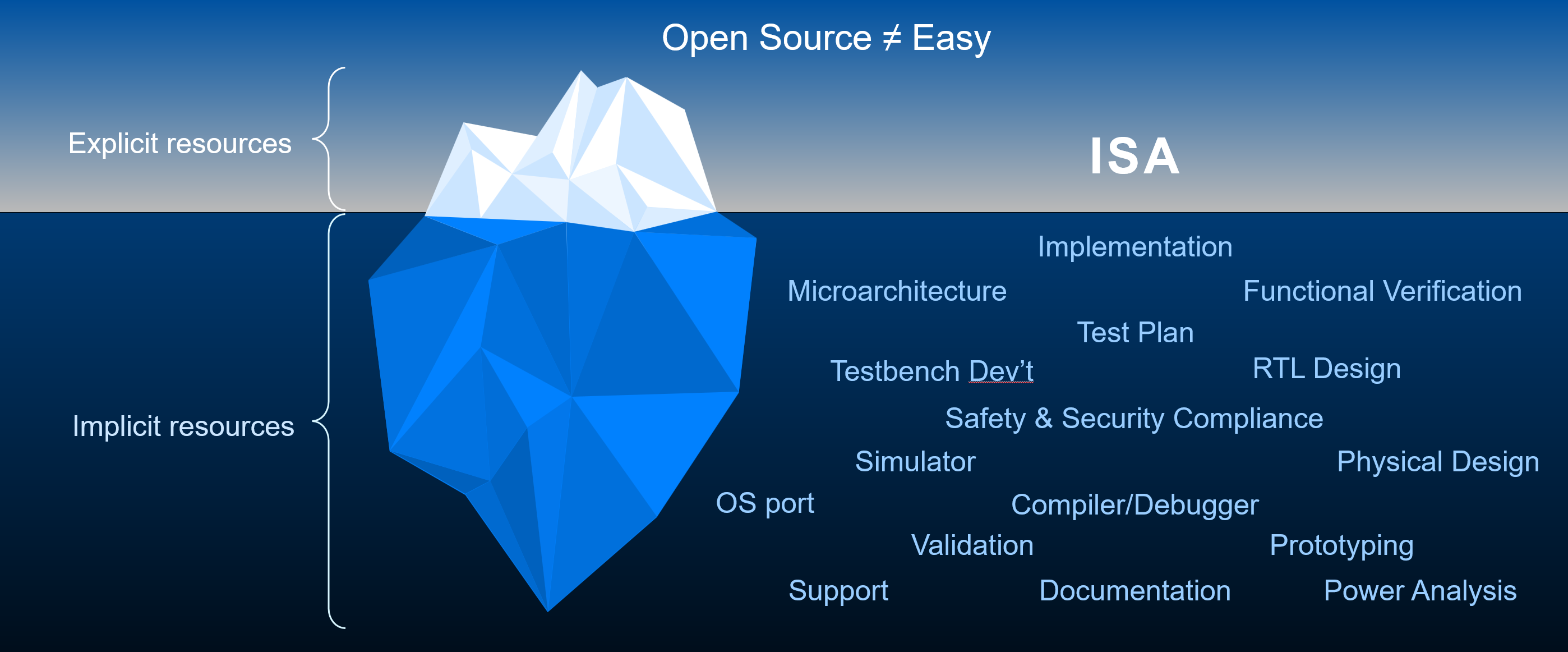

ARC-V is more than the latest choice for RISC-V processor IP – Synopsys provides more chip and software development stack pieces in a comprehensive approach. Rich Collins, Director of Product Management at Synopsys, shows a powerful visual indicating that developers tend to see RISC-V processor IP as just the ISA but maybe not the whole set of implicit resources lurking beneath the surface that can make or break a RISC-V implementation.

“The implementation is where the rubber meets the road,” says Matt Gutierrez, Sr. Director of Marketing for Processor & Security IP and Tools at Synopsys. “The fact that RISC-V is an open standard does not mean it’s free – it comes down to the investment and expertise required to implement it.” Synopsys is aiming to help its customers bring ARC-V processor IP to life with two thrusts: customizing and optimizing the processor core for an optimal power-performance-area (PPA) footprint with better odds for first-pass silicon success, and bringing application software up on the new part.

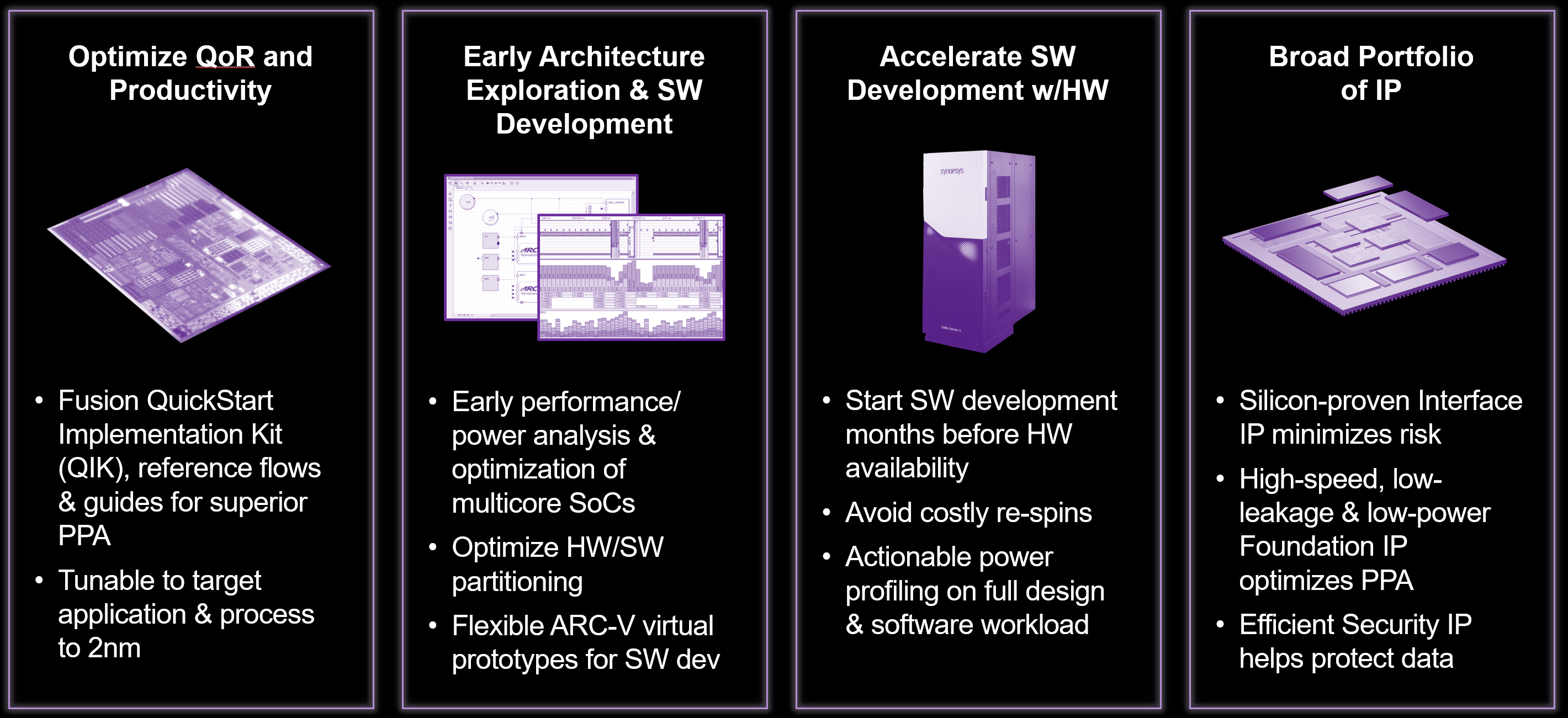

RISC-V designers with limited experience creating chips will likely need help placing advanced cores in chip designs destined for advanced process nodes. Synopsys has its Fusion QuickStart Implementation Kit, multicore-enabled architectural exploration tools, FPGA-based prototyping for early software development, and a portfolio of IP to surround an ARC-V core in a real system-on-chip.

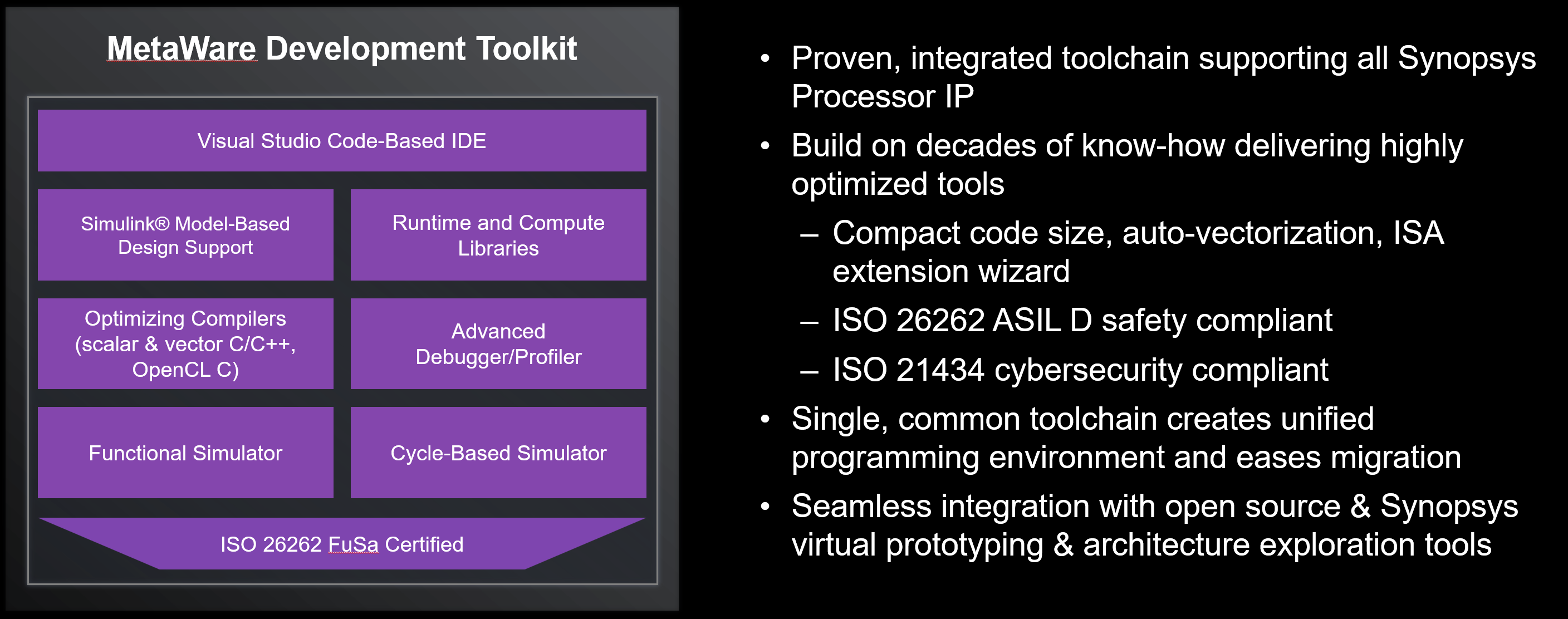

Synopsys also offers the MetaWare Development Toolkit, updated for RISC-V support, with a software development toolchain including compilers, profilers, and simulators. Synopsys immediately has proven SDKs for ARC-V and RISC-V software developers by porting its mature and optimized ARC tools and libraries. One interesting item in the toolkit is ISO 26262 functional safety (FuSa) support and certification, which appears prominently across the ARC-V families.

ARC-V portfolio highlights scalability, FuSa, and vector math

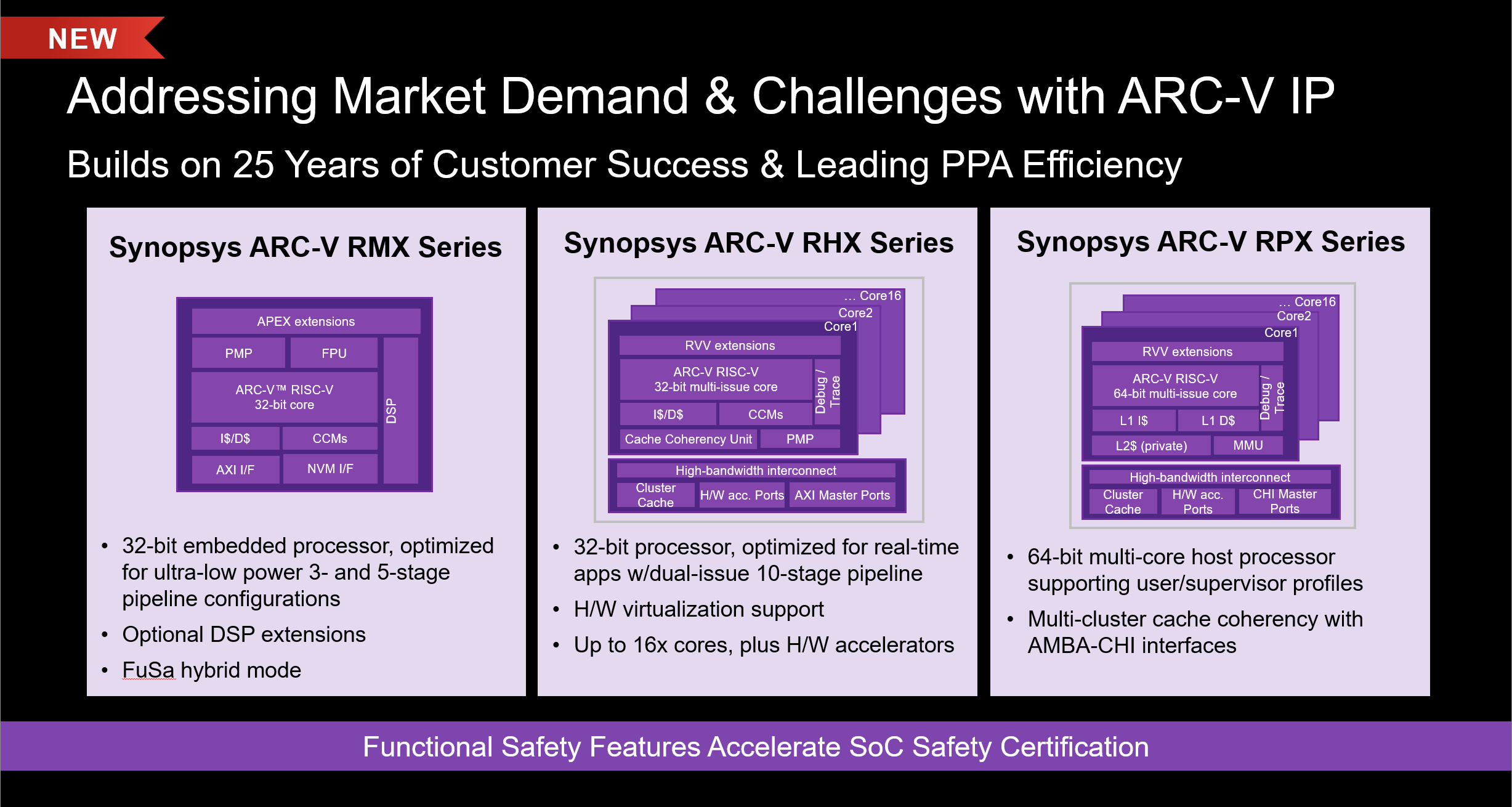

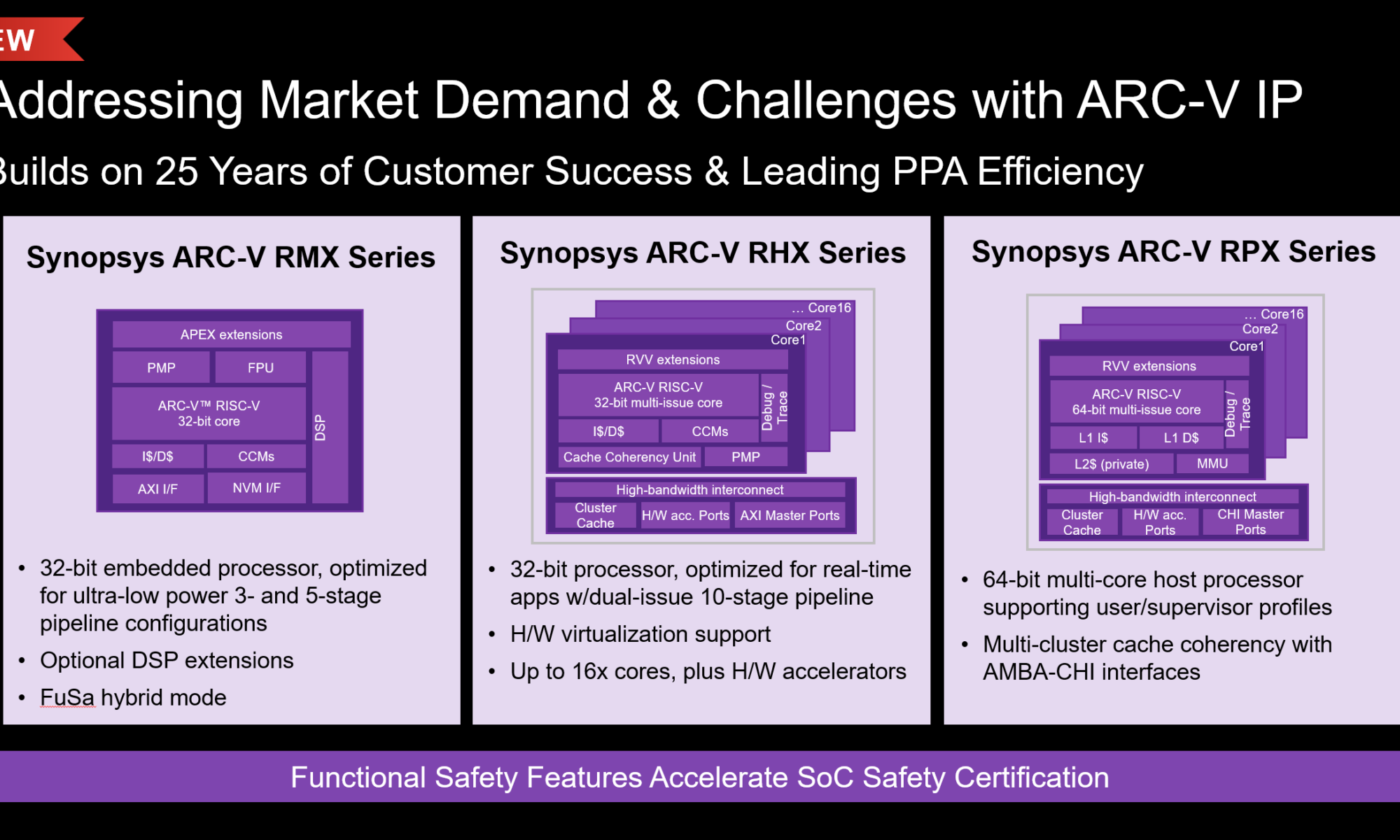

Collins introduced the ARC-V portfolio by positioning the new IP series in the same three tiers – embedded, real-time, and host – as the existing ARC IP series. Illustrating why they are making this move, the ARC-V offering sets up several clean choices in scalability with a choice of core IP starting points.

- The embedded tier focus is power efficiency in single 32-bit RMX cores, with an ultra-low-power 3-stage pipeline or a still efficient 5-stage pipeline for more performance. There is also a clean break for either FuSa or DSP support.

- The real-time tier features 32-bit RHX engines with a deeper 10-stage pipeline and multicore support, adding a similar clean break between FuSa or vector math support available in RISC-V with RISC-V Vector (RVV) extensions.

- The host tier offers 64-bit RPX engines supporting complete memory management, multi-cluster cache coherency, and a clear choice between FuSa and RVV support.

The ARC-V portfolio and the surrounding software strategy are strong statements from Synopsys. While they emphasize that the existing ARC families continue their availability, the new emphasis on the ARC-V processor family makes it easier for customers to choose where they land and move back and forth between choices if needed. RISC-V flexibility means customers can customize and extend ARC-V cores to add their proprietary value, a carryover of the philosophy behind ARC since its introduction. The ARC-V RMX embedded processor series should be available soon, with the RHX real-time and RPX host processor series to follow.

See more about Synopsys’ ARC-V strategy in an article from Rich Collins:

How the RISC-V ISA Offers Greater Design Freedom and Flexibility

Also, listen to the SemiWiki podcast episode with host Daniel Nenni:

Podcast EP212: A View of the RISC-V Landscape with Synopsys’ Matt Gutierrez

Comments

There are no comments yet.

You must register or log in to view/post comments.