I decided to attend a webinar today hosted by Synopsys, “Streamline Your PrimeTime ECO Flow For Fastest Setup, Hold and Timing DRC Closure.” The format was to present slides first then hold for questions until the end. Enough time was spent on questions which made this webinar different than most other webinars I’ve attended. The on-demand webinar is here.

David Guinther announced the webinar and noted the DATE conference in Germany had Synopsys users presenting. The next webinar in the series is called “Faster Timing Signoff” scheduled for April.

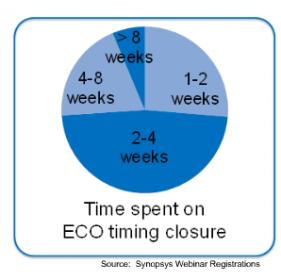

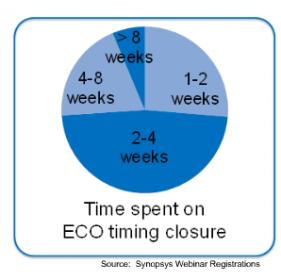

How much time are you now spending on ECO timing closure?

I was surprised to find out that some design groups spend over 8 weeks on ECO timing closure.

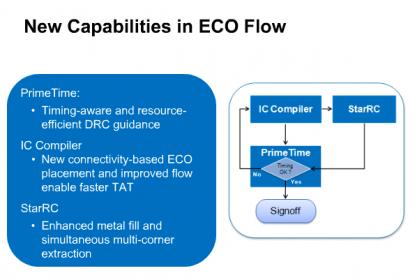

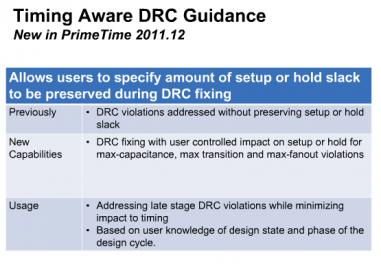

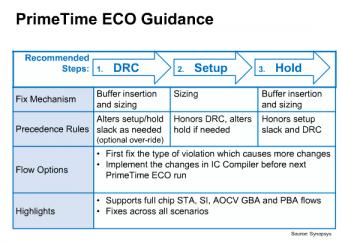

Vivek Ghante talked next about new DRC guidance features, and the recommended ECO flow with ICC, PT and StarRC.

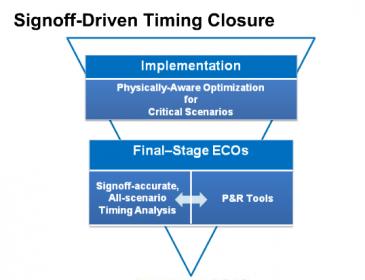

Even after constraint-driven P&R there are still timing violations.

New capabilities in ECO Flow:

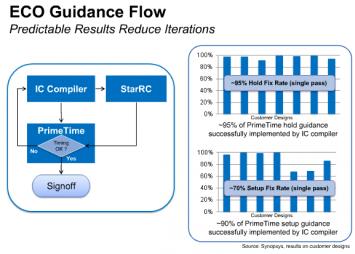

This closure loop can be shortened by following our recommended usage. 2011 webinar… (Broadcom, Qualcomm, TI users).

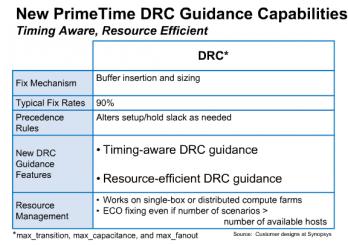

One approach to fix timing is buffer insertion and sizing with a 90% fix rate.

Setting timing margins does impact the ability of DRC fixing.

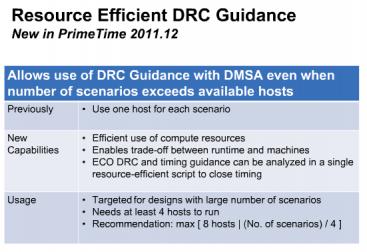

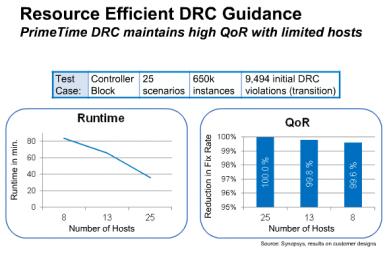

Modern designs can have tens or hundreds of scenarios. So how do you run these efficiently?

Resource Efficient DRC Guidance.

ECO guidance flow – even with just one loop there is 95% hold fix rate and 70% setup time fix rate. Add more hosts to speed up your results:

PrimeTime ECO Guidance Flow using: IC Compiler, StarRC and PrimeTime:

Follow these tool steps for best results:

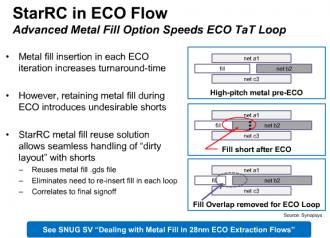

If metal fill fixes cause a short, it gets fixed automatically:

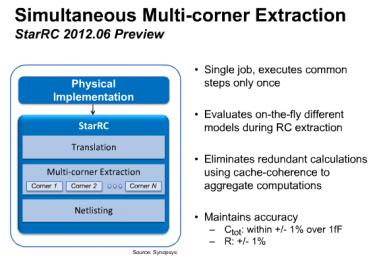

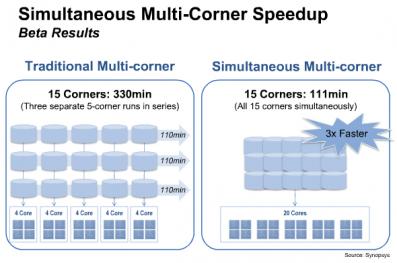

Multi-corner extraction: 5 corners typically extracted at 40nm, however now with more corners you need a way to speed up the runs.

Simultaneous multi-corner extraction – coming this summer and will speed up run times for extraction. Results are within 1% of previous.

Speedup of 3X are typically seen in the Beta results.

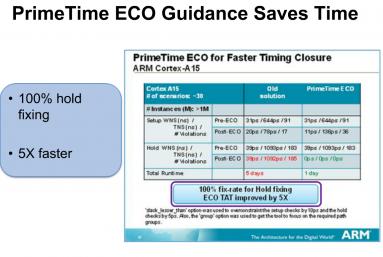

SIG results from ARM show a 5X speed up:

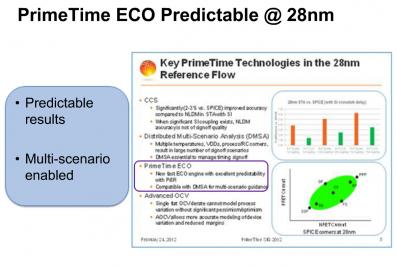

GLOBALFOUNDRIES is using this new flow at the 28nm node:

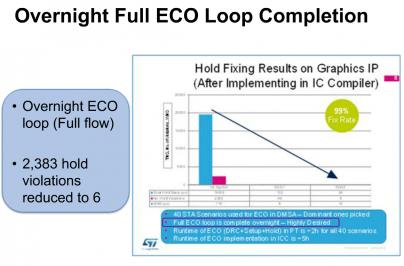

ST can run an ECO flow overnight.

Questions and Answers

Q: How to pick library cells for hold fixing?

A: Pick a representative set of buffers and delay elements.

Q: Is the new DRC fixing included in my licenses?

A: Yes, this is all included in PrimeTime SI.

Q: How does PT ECO resize cells and rename?

A: For resize cells the original name is used, for inserted buffers it uses U1, U2 etc. You can set a custom prefix.

Q: During late state changes we want to skip DRC violations and focus on uncoupled max transitions. Can we do that?

A: Max transitions looks at skew effects. You can set a variable to remove some delta crosstalk checks.

Q: Can you give guidelines on how long PT will run with 10 to 15 million instances?

A: It depends on several factors like design size, number of clocks, number of violations, size of violations, number of scenarios. Start with an optimized netlist, use default settings, have enough disk space, setup your libraries. Typical ECO run is longer than an SI run.

Q: I thought Star RC had multi-merging corners. How is this different?

A: Yes, there was a merged corner flow in Star RC. Now in simultaneous extraction we are using distributed processing to improve TAT, all corners are being calculated at the same time per polygon.

Q: How much faster is the IC Compiler incremental placement flow?

A: From 10X to 20X, plus improved QOR.

Q: Can PT ECO be used with other implementation tools than IC Compiler?

A: For best results use IC Compiler, although the output is a Tcl file which can be used by other tools as well.

Q: I have several modes and corners, will the ECO changes in one mode be carried over to other modes?

A: When we do ECO changes all netlists must be the same. All the other modes and corners see the same changes.

Q: Do I need to generate new XTRG files for simultaneous multi-corner extraction?

A: No.

Q: What’s the best way to remove timing violations after multiple passes through the ECO flow?

A: Start with an optimizing P&R netlist. If large number of timing violations then you may require more than one pass to get closure. If still a small number of violations left, then go back to ICC and try additional optimizations. There could be a few manual changes required.

Q: What is the effect on the overal ECO flow with the new ECO placement?

A: WIth a 10X to 20X run time improvement you are able to get through the whole process quicker, with fewer loops. A 6 million instance design at 40nm we saw a 2X run time improvement with this new ECO flow.

Q: Can PT create hold timing scripts?

A: Use PT in DSMA mode, so that violations fixed in one scenario are not violated in another scenario.

Q: When ECO cells are placed, will the existing routing be preserved?

A: Yes, you can preserve routing with a simple option. For TCL-based editing you can also do this.

Q: At what stage do we run ICC and StarRC loop? Do we need to do ICC optimization?

A: Yes, first optimize the design in ICC. Then do final stage ECOs in PT. Changes suggested by PT need to be implemented in ICC.

Q: Can we overfix violations?

A: In general the DRC fixes are done without adding new violations, there is no way to remove margins on DRC rules.

Q: Can PT fix glitches?

A: We do setup and hold time fixing now, for static noise analysis there is no capability in place yet.

Q: Does the number of RCs in the topology change for each corner?

A: Yes, with simultaneous extraction all corners are extracted at once, so the number of elements are always the same per corner.

Q: Is the output from PT to ICC in text?

A: Changes for Size cells and buffers are in text as Tcl code.

Q: The number of RC are similar or same?

A: Exactly the same number of RC elements across all corners.

Registrant Stats:

Modes and corners: 25% use 1-2 corners, 50% 3-5 corners, remaining 6+ corners.

DMSA and PT ECO: over 50% using DMSA analysis. About 25% complete their first design with new ECO features.

Closing timing about 4.6X faster using the new approaches.

Presenters

Tzong-Maw Tsai

Tzong-Maw Tsai

Director, CAE, Implementation Group

Synopsys Inc.

Tzong-Maw Tsai is the CAE Director for timing signoff products and customer engagement support at Synopsys. Tzong-Maw and his organization are responsible for supporting PrimeTime performance, signal integrity, delay calculation and ECO flows. He has been with Synopsys since 1992 and was responsible for logic synthesis and physical implementation products prior to his current role. Tzong-Maw received his BS degree in Electrical Engineering from the University of Rochester, Rochester, NY.

Vivek Ghante

Vivek Ghante

Staff Corporate Applications Engineer, Implementation Group

Synopsys Inc.

Vivek Ghante is a Senior Corporate Applications Engineer at Synopsys supporting PrimeTime. His focus is tool performance, ECO flows and HyperScale technology. Before moving into EDA in 2003 he was responsible for CPU physical implementation. While at Synopsys he’s worked on the Design Compiler team and has driven customer flow evaluation and improvement projects. Vivek received a BS in Electrical Engineering from the University of Texas at Austin; his MBA is from University of California, Berkeley.

Summary

ECOs are a fact of life in the design world and at the end of a long IC design project you want all the flexibility to change your design and yet get into tapeout quickly. The new ECO flow from Synopsys does deliver TAT improvements that will help your project. An all Synopsys tool flow was promoted in the webinar however you can use other P&R or extraction tools as well.

Comments

0 Replies to “Timing Closure for ECOs in your SOC Design”

You must register or log in to view/post comments.