Last year, you could claim (like I did in this blog) that Cadence was making money with large VIP port-folio, when Synopsys was managing sales of a large Design IP port-folio (thanks to a successful acquisition strategy in the 2000’s). But the latest acquisitions made by Synopsys of VIP centric companies like nSys or ExpertIO should have warned us (and Cadence, by the way): the EDA and IP centric company is investing the VIP field! After the acquisitions time come the new product launch, today the market is discovering… Discovery.

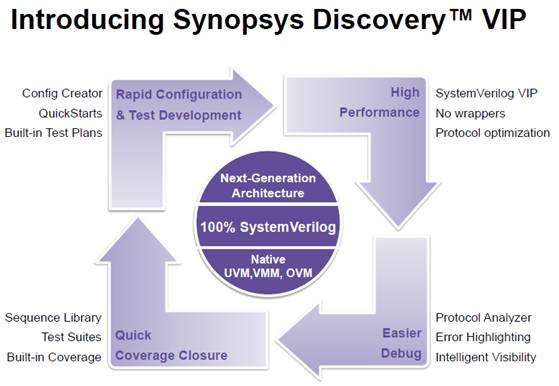

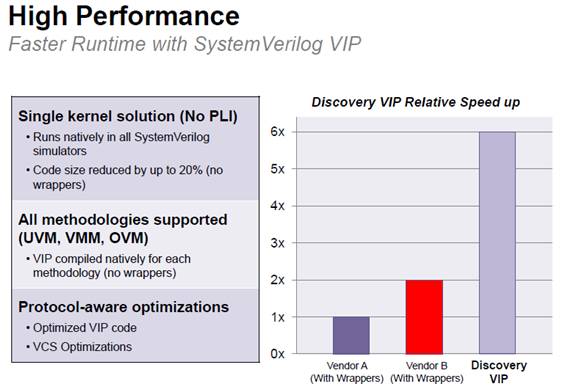

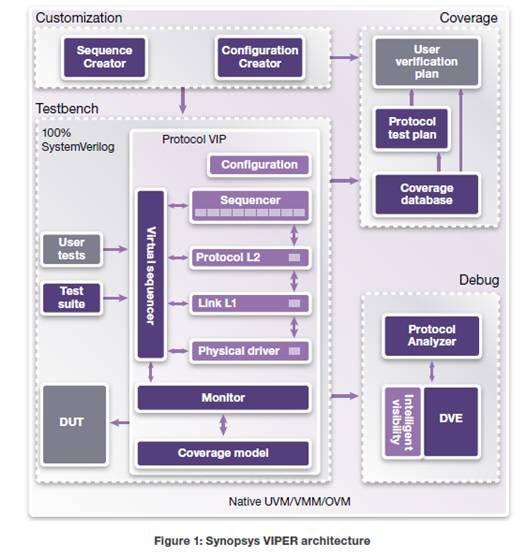

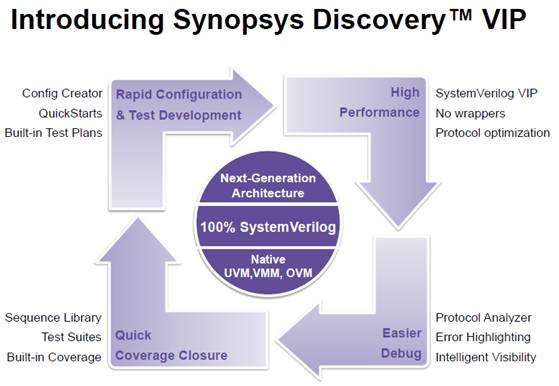

It looks like this product launch is a real offensive, and much more than just an announcement. Synopsys Discovery VIP is written entirely in SystemVerilog, includes native support for UVM, VMM, and OVM, and is compatible with all related verification environments… and supports all major simulators, including Cadence Incisive (!), the product realizes a breakthrough in the VIP jungle. Because of the multiple competing above mentioned standards (UVM, VMM and OVM), the only way to support all of these (and it was a strong market requirement) for a VIP product was to use wrappers. By using wrappers, on top of making the product inelegant, you made it slower. Diminishing simulation run time, offering a performance improved by 3 to 6X is a strong sales argument, I am sure that Synopsys’ sales force will be the first to benefit from this argument, the second being the customers!

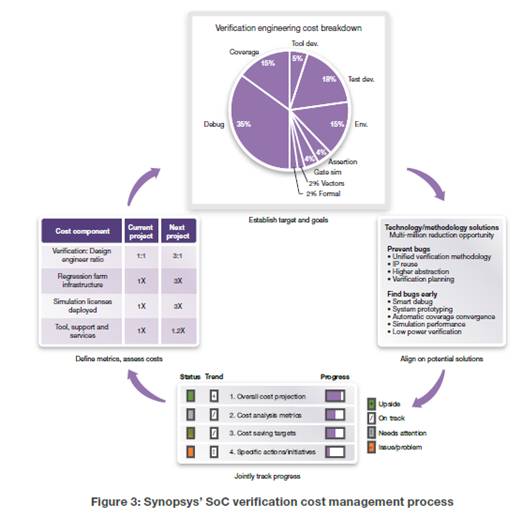

Such an argument is based on an identified issue, that every design team trying to complete a SoC design, every marketing team fighting with Time To Market issue, every shareholder expecting a high return on investment knows very well; the cost and elapsed time due to Verification. In fact, I am not so sure that the basic shareholder understands anything about Verification, but he should understand ROI! The next picture is useful to understand the cost breakdown associated with Verification. If you look at the middle left box, you see a 3X cost (or license count, or resources) increase for almost every task (except “Tool, Support and Service” with 20% only, so I suspect that Synopsys will sell Discovery 20% higher than the previous solution?). So, offering a 3 to 6X run time improvement is welcome, to keep the design schedule and consequently the time to market within reasonable limits.

If you look at the product itself, Synopsys includes with Discovery VIP, a Protocol Analyzer which enables engineers to quickly understand, identify and debug protocols in their designs, and debug and coverage management features, so the complete solution is built within a single product.

If we look to Synopsys VIP port-folio, we can see that the war with Cadence will be face to face, protocol by protocol, as they both address the same customer needs. Except for the Memory Models, that Cadence is marketing after Denali acquisition, and where Denali had a monopoly for a long time, but on what constitute the Verification IP market, still to be evaluated, but probably in the $100 to $150 million range, we can expect to see an interesting battle. I am just waiting to know what will be Cadence’ answer to Synopsys’ Discovery offensive!

From Eric Estevefrom IPnest

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.