Mentor Graphics, a Siemens Business, has completed their acquisition of EDA company Avatar Integrated Systems. I recently spoke with Joe Sawicki, Executive VP of the Mentor IC EDA segment, about the acquisition strategy and IC Design platform goals for integration of the Avatar products.

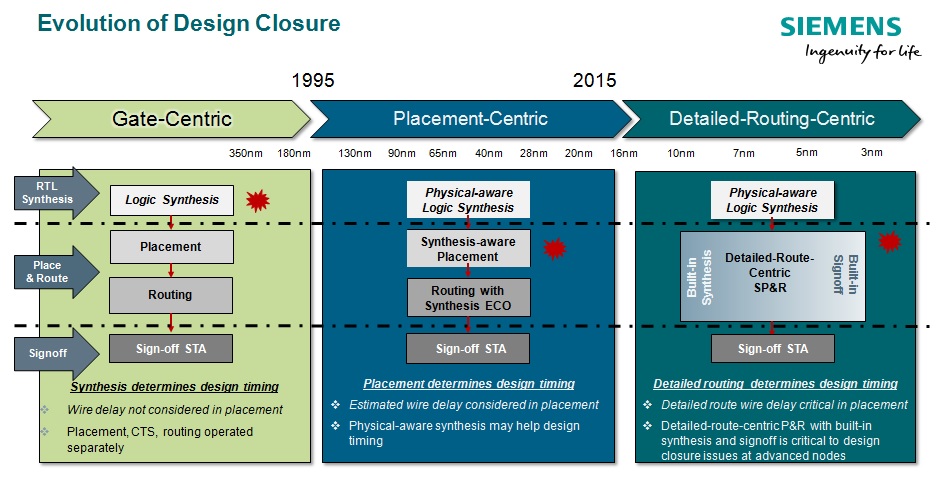

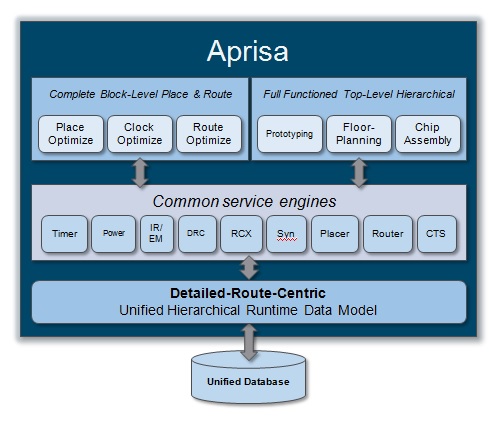

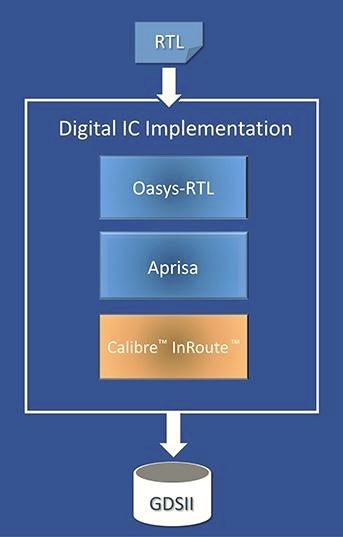

Avatar (formerly ATopTech) focused on physical implementation tools for complex, digital SoC designs – e.g., floorplanning, placement, clock-tree synthesis, routing, and ECO flows. Specifically, the foundation of the Aprisa Product was to build their physical algorithms on a route-centric, hierarchical data model. The right-hand side of the figure below highlights the Avatar strategy.

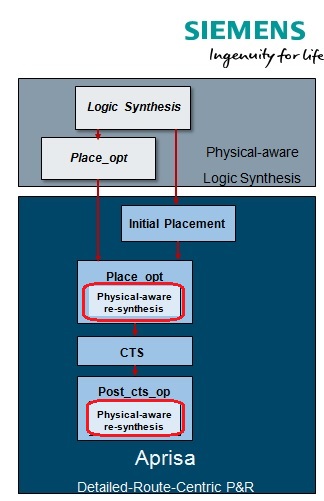

The Aprisa SAPR input data is a simple LEF/DEF design model from a (physical-aware) logic synthesis toolset. From the synthesis netlist, Aprisa applies optimizations that focus on ensuring subsequent routability – e.g., congestion avoidance, pin access, adherence to multipatterning decomposition coloring. An internal physical DRC verification engine is applied. A diverse set of clock tree design styles are available, including useful clock skew timing optimizations throughout.

An internal synthesis engine allows for further optimization. The input netlist placement assumptions may not accurately reflect the route impact of congestion, R*C delays, and clock skews. Logic restructuring based on the routing model may be needed. The tool incorporates static timing, noise, IR, and EM analysis algorithms to guide placement and route assignment decisions.

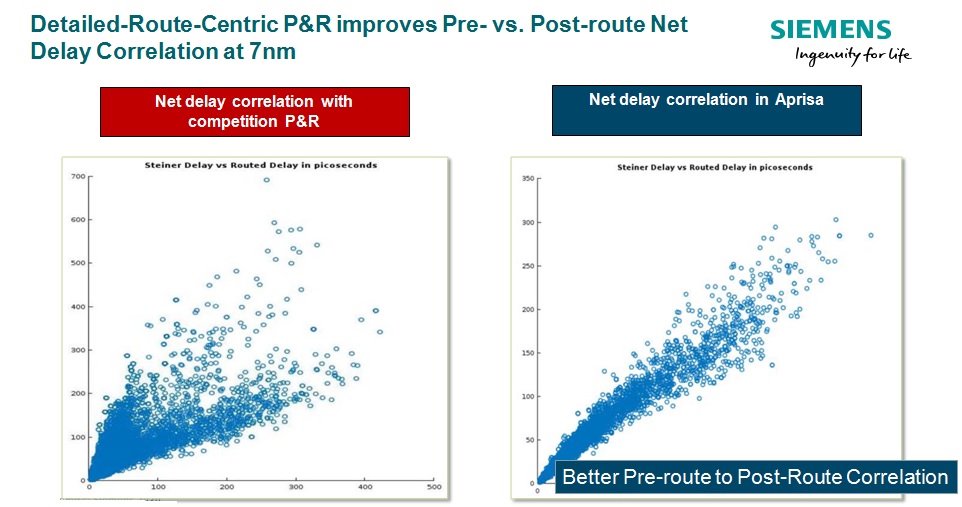

Joe indicated, “Designers of complex SoCs at advanced nodes are seeking the following from their APR flow – better synthesis-to-post route timing correlation, no coupling noise issues, no DRC violations, in short, fewer APR iterations and faster time to closure. We benchmarked Aprisa, and found the PPA results to be excellent. The learning curve was extremely quick. We had competitive evaluation data within a few weeks.”

The figure above illustrates the pre-route (Steiner estimate) to post-route timing correlation on the Mentor benchmarks at the 7nm node.

Joe then described the IC Design product strategy. “The Nitro-SoC platform will be supported through the 16/14nm node. Going forward, Aprisa will be the SAPR solution for 7nm and below. The DRC engine that was internal to Aprisa will be replaced by Calibre InRoute.”

Joe continued, “The strength of the combined engineering and support teams will offer roadmap stability and continuity to customers, who may have been anxious given the relatively small size of Avatar’s team. Mentor will leverage its relationship with the foundries to extend the Aprisa product certification for advanced process nodes.”

With regards to the competitive position of the new offering, relative to the integrated platforms available for physical implementation, Joe said, “Designers want an APR tool that is feature-rich and easy to use. The route-centric data model and optimization algorithms in Aprisa provide faster closure and signoff accurate results. The use of a physical-aware (placement-centric) synthesis flow is a good start, but the set of optimizations available is a key differentiator, specifically route-aware logic re-synthesis. Refinement is where you get considerable value. We’ve already flipped customers from other products.”

It will be interesting to track how Aprisa emerges in the reference flow certification from the foundries, and how the route-centric with logic re-synthesis methodology evolves as a point tool solution. Mentor’s acquisition of Avatar expands the scope and future development of SAPR offerings. More competition among EDA providers is always a good thing for the IC design community.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.