LVS Challenges at Advanced Nodes

Accurate, comprehensive device recognition, connectivity extraction, netlist generation and, ultimately, circuit comparison becomes more complex with each new process generation. As the number of layers and layer derivations increases the complexity of devices, especially Layout Dependent Effects (LDE), becomes harder and harder to model. One of the keys to design success in 40nm and 28nm is to enable customers to easily modify foundry rule deck to include their own device models for transistors, resistor, capacitors, inductors, etc., and even augment the deck with their own checks.

iLVS—A More Standardized Approach

To address this situation, TSMC and Mentor Graphics have collaborated to define iLVS, a syntax that provides customers with a more easily adaptable solution to their circuit verification needs. Using iLVS, users can more easily modify and augment foundry rule decks, yet still adhere to the modeling and manufacturing intent captured in these decks.The goals of iLVS are to improve technology data integrity while reducing duplicate development effort. iLVS supports multiple EDA tools, which makes it easier for customers to adopt new EDA vendor innovation in the form of optimized tool implementations. It also makes it possible for customers to take advantage of these innovations and enhancements earlier. At the same time, iLVS makes it easier to customize LVS rule decks to accommodate users’ own unique device definitions or to introduce specialized checks.

iLVS Architecture

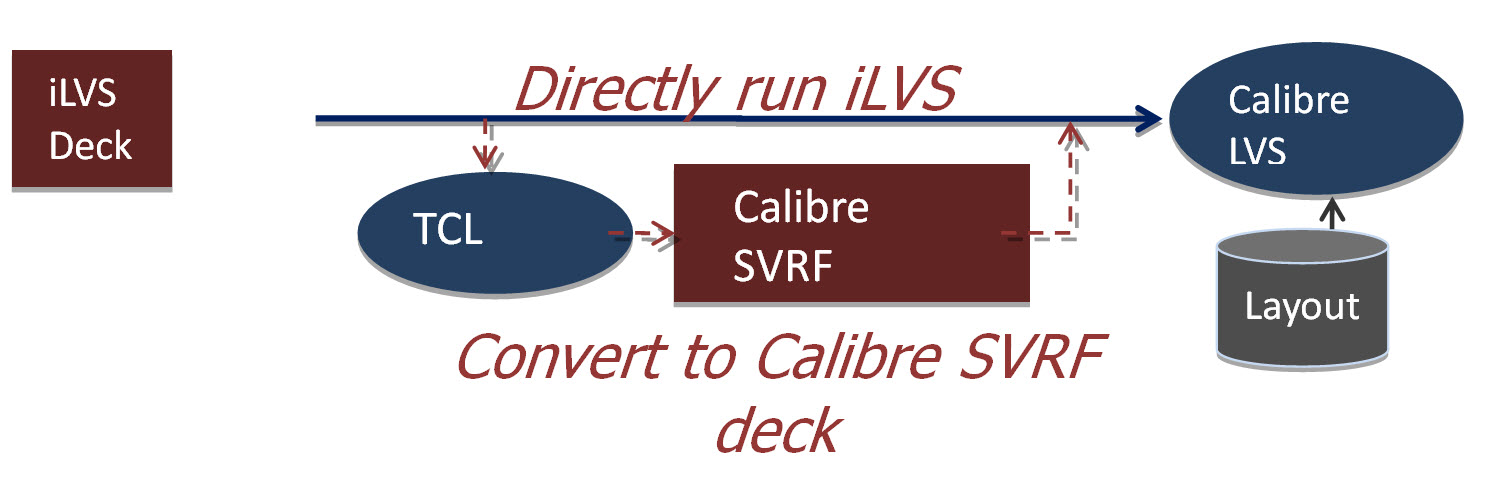

An iLVS rule deck is implemented with the Tcl scripting language, which calls a set of standardized library functions that are common across different tools. The library is a superset of the most commonly used LVS operations. At the implementation level, each tool vendor implements the standard functions using the tool’s native language syntax. This allows vendors to optimize the executable code for best accuracy and performance, while shielding the rule deck developer from the details of the tool implementation.iLVS is non-intrusive in that it can be introduced without changing the user’s current design methodology and flow. Everything a user needs to adopt iLVS—the TSMC iLVS rule deck, the standard functions library, and the vendor implementation library—is available as a package download from TSMC.

Transitioning to iLVS

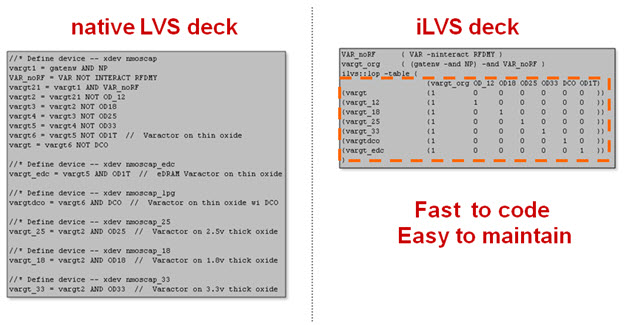

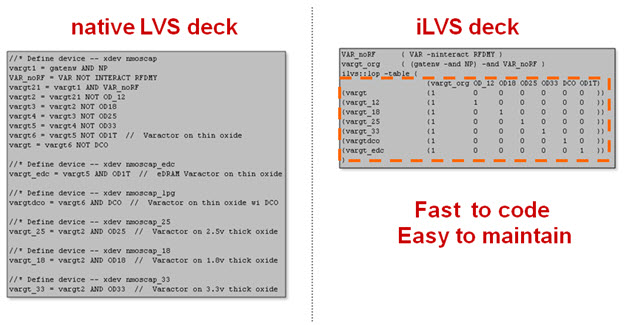

To make it easier for users to define their LVS devices, iLVS uses a device truth table to add and modify devices. This typically simplifies the rule deck by converting many Boolean functions into a single truth table for a class of devices. It also makes the deck easier to maintain. To enable a smooth transition from existing LVS decks to iLVS, the syntax allows customization through “in-line” calls to unique tool functions. In this way the majority of LVS checks can be handled by standard iLVS syntax, while a user’s unique operations can be maintained in the same deck. Specialized electrical rule checks can be handled in this manner for example.iLVS decks are now available from TSMC for 65GP, 65LP, 40G, 40LP, 28HP, 28LP, 28HPM and 28HPL processes, and 20G is in the development pipeline.

Authors: Carey Robertson, Mentor Graphics and Willy Chen, TSMC

This article is based on a joint presentation by TSMC and Mentor Graphics at the TSMC Open Innovation Platform Ecosystem Forum. The entire presentation is available on line on theTSMC web site (click here).

Share this post via:

Comments

0 Replies to “iLVS: Improving LVS Usability at Advanced Nodes”

You must register or log in to view/post comments.