Earlier physical optimization impacts a design QoR gain and can disclose potential hurdles in dealing with unknown design variants such as new IP inclusion or new process node issues. Along the RTL-to-GDS2 implementation continuum, a left-shift move requires a robust modeling and proper context captures in order to produce meaningful outcomes.

Earlier physical optimization impacts a design QoR gain and can disclose potential hurdles in dealing with unknown design variants such as new IP inclusion or new process node issues. Along the RTL-to-GDS2 implementation continuum, a left-shift move requires a robust modeling and proper context captures in order to produce meaningful outcomes.

Aside from synthesis, floorplanning, placement and routing are three major optimization segments that largely shape the final design footprint and determine the feasibility of design targeted performance. Although judging on its own merits, each has a unique set of pre-requisites and its optimization context, close alignment among them is crucial.

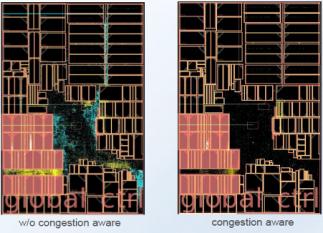

The floorplanning step involves applying an optimal strategy for top-level placement on the given budgeted area without incurring complication for downstream implementation steps. For example, having a robust IP or macro placement that honors a uniform data flow and accomodates adequate repeater staging area or track allocation, should provide a better chance of placement and route convergence as it will prevent congestion risk and unmanagable area increase.

Similarly, during the place and route step, preserving the optimization intent achieved in earlier synthesis and driving further gate level QoR’s (Quality of Results) is key to ensure predictability in design closure convergence.

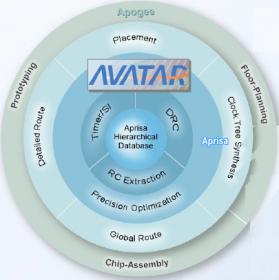

Avatar Physical Implementation Solution

Aprisa and Apogee are two physical design related products from Avatar Integrated Systems (previously known as AtopTech). Aprisa is a complete P&R system which includes placement, clock tree synthesis, optimization, global routing and detailed routing. It has embedded analysis engines that correlates with foundry-approved sign-off tools and supports standard formats for its collaterals (Verilog, LEF/DEF, Liberty, SDC and GDS2). It has been certified for 16/14/10nm and 7nm.

Apogee is a top-down hierarchical prototyping floor planning and chip assembly tool. It enables fast analysis of design hierarchy and automates many manual tasks such as macro placement and blockage creation to ensure faster convergence to an optimal floorplan.

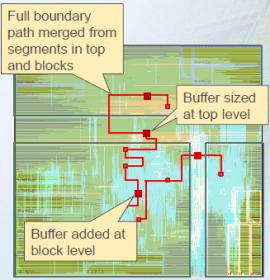

Both tools shares a common analysis engine and database that ensures tight correlation between block and top level timing. Avatar’s In-Hierarchy-Optimization (iHO), intended to help top-level timing closure without either the traditional black-box modeling or flattening step, is an example of many patented technologies incorporated in both tools specifically developed to address increased design challenges in advanced process nodes.

Floorplanner and Placement

Apogee handles complex floorplan criteria such as rectilinear regions, multi-height cells and mixed/overlapping sites. Both channel based and channel-less floorplans are supported. It has an automatic placement blockage generator and a macro placer with grouping and legalization capabilities. To aid for data flow analysis, the GUI has both hierarchical flyline analysis and logic-vs-layout cross-probing features. With its unified architecture and hierarchical data model, it comfortably handles multi-million gates design and easier hierarchical ECO with continued 2x to 3x runtime improvement per major version refresh.

Aprisa´s placement technology is a timing and congestion driven analytical based placer, which keeps track of real time TNS and congestion overflow –to automatically adjust timing and congestion parameters for an optimal QoR or runtime tradeoff. Aside from the standard cost factors (such as wire-length, area, leakage power, etc.), the adaptive placement and optimization engines take into account critical dependencies such as pin accessability. It has automatic neighbor rule as well as user’s controlled version to allocate cell spacing for pin access.

Aprisa features a partition-based optimization mode that allows intelligent path clustering based on timing criticality. Such method is intended to achieve a more efficient thread allocation and multi-thread scaling for subsequent optimizations. Its power optimization features include switching activity optimization, OCV aware placement, useful skew handling and always-on buffering/retention cell placement. Both UPF and CPF constraints are supported for low power-driven optimization.

MCMM Analysis, CTS and Timing Analysis

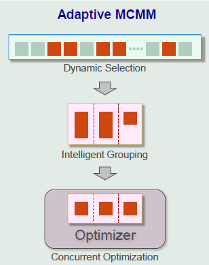

Aprisa has native and adaptive MCMM (Multi-Corner Multi-Mode) approach that automatically groups scenarios and analyzes them in mixed sequential/multi-threaded mode, yielding an optimal balance of memory usage and run time. It supports various on-chip variation methods (AOCV, LOCV, POCV and LVF).

Aprisa´s progressive MCMM CTS handles various scenarios for complex designs such as based on skew-group, slack-driven, multi-point; mesh and H-tree; power aware clock tree optimization with useful skew; cluster-based clock trees or meshes; auto clock-gate cloning/decloning, etc. The CTS engine balances clock trees for all modes and corners while allowing flexibility to leverage skewgroup information to further optimize the clocktree. The route-based clock tree optimization minimizes the use of buffers, automatically create special routing constraints (such as double-width/spacing/via, shielding, route layer, etc.) and matches latency targets given by user for any pins. It is accompanied by a GUI for visualizing, cross-probing and real-time intervention such as clock buffer resizing or moving clock buffer or leaf cell to different level of the hierarchies.

Aprisa´s progressive MCMM CTS handles various scenarios for complex designs such as based on skew-group, slack-driven, multi-point; mesh and H-tree; power aware clock tree optimization with useful skew; cluster-based clock trees or meshes; auto clock-gate cloning/decloning, etc. The CTS engine balances clock trees for all modes and corners while allowing flexibility to leverage skewgroup information to further optimize the clocktree. The route-based clock tree optimization minimizes the use of buffers, automatically create special routing constraints (such as double-width/spacing/via, shielding, route layer, etc.) and matches latency targets given by user for any pins. It is accompanied by a GUI for visualizing, cross-probing and real-time intervention such as clock buffer resizing or moving clock buffer or leaf cell to different level of the hierarchies.

Aprisa includes a fast timing analysis engine with many advanced features. Based on Avatar rating, it takes 5 minutes per million instances. It supports SDC parsing, native OCV timing analysis, CRPR (Clock Convergence Pessimism Removal) and a timing browser

Routing

Routing

Addressing first-order effects of SI (Signal Integrity), EM (Electro Migration) and metal-fill emulation with near detail route level accuracy during global route stage is key to its success in delivering targeted detail route outcomes. Aprisa’s fast global route engine was rated to route millions of nets in minutes. It supports multi-threading and routes 250K instance in about 5 minutes on an 8 CPU machine. The global route includes track assignment that facilitate delays and signal integrity assessment.

Aprisa’s detailed router is a hybrid technology, which support both gridded routing as well as off-grid pin routing when needed. According to Avatar, unlike the other routers’ handling of DRC as an afterthought, Aprisa handles all the DRC violations during route optimization. This includes handling complex design rules (such as EOL spacing or extension, minimum enclosure, etc.), special routing rules (such as double spaced, shielding, double vias, etc.) and DFM related issues (such as wire-spreading, double-vias).

For advanced nodes, Avatar’s router uses its own patented color-aware DPT routing technology to enable DPT compliant routing and also support CM (Cut-Metal) routing methodology. As resistance is more prevalent in advanced process nodes, Aprisa’s router has the capability to minimize jogging for lowering via usage and accounts for high-R layer usage in pre-route RC estimation as well as in detail routing for better timing. It automatically promotes critical net to high-metal layer while leveraging low-resistive wire for long nets connection to reduce buffer usage. Tight timing correlation is also maintained throughout the process including between pre-route and post detail route steps.

The resurgence of Avatar’s physical design solution has added color to the IC physical implementation landscape. An integrated solution that aligns both the optimization and analysis engines while managing proper contexts using a unified data model can deliver enhanced QoR’s. Aprisa and Apogee seems to have demonstrated such leverage.

For further details please check here: Aprisaor Apogee.

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center