Large SoC design teams typically have a cadre of project managers to oversee all facets of functional verification — e.g., specification, reviews, directed testbench development, automated (pseudorandom) testcase generation, HDL coverage measurement and reporting, and bug identification/tracking database management. The relatively small engineering teams developing analog/mixed-signal IP commonly have little of that infrastructure at their disposal. The designer of an analog sub-block macro is usually also its “verification lead” and its “project manager”. The platform is a Spice-like circuit simulator. Each macro within the IP block is characterized by a set of measurement targets (or acceptable target ranges) — those specifications define the validity of the design. There is currently a dearth of tools available to assist the AMS IP designer with the PM aspects of verification, and ultimately sign-off.

I recently had the opportunity to chat with Nicolas Williams, Product Marketing Manager at Mentor, a Siemens company, about this AMS IP verification task. Nicolas described a component of the Tanner EDA tool suite — Tanner Designer — developed specifically to aid with analog verification project management.

.measures

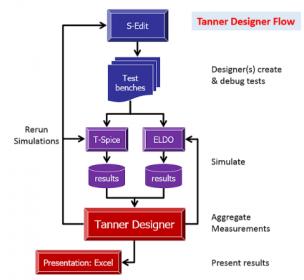

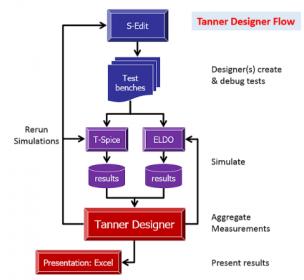

The general flow for using Tanner Designer is illustrated in the figure below.

The setup is straightforward. The analog designer directs Tanner Designer to the (hierarchy of) IP block and macro component simulation results directories. Tanner Designer pulls measurement results from the analog simulations into a database, from which the project “dashboard” is presented. These measures can originate from schematic properties or be added as part of the simulation flow. Although the flow diagram above focuses on Mentor tools, a recent feature add for Tanner Designer (Release 2017.2) supports the import of measurement data from other sources, such as other simulators or test equipment, to provide an easy-to-use (Windows) environment for analog IP project management.

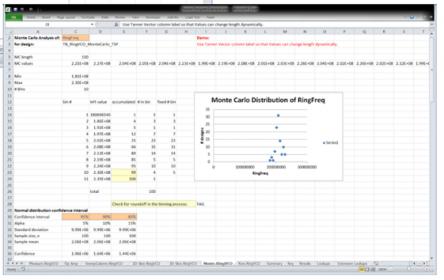

Dashboard and Excel

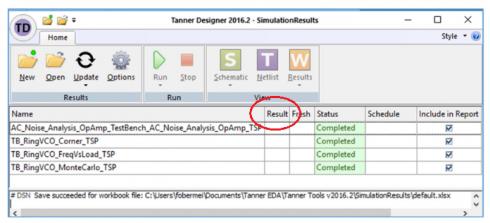

The graphic below is a screenshot of the Tanner Designer dashboard, which tracks each simulation testcase status, aggregates the data, and serves as the interface to Excel for calculation and final reporting of the comparison between specification and simulation results.

Tanner Designer dashboard, and corresponding Excel spreadsheet

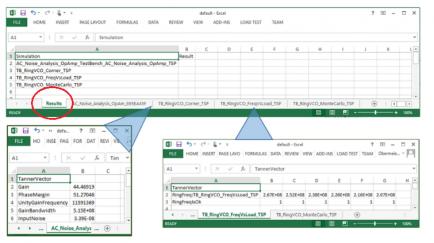

Individual analog macro simulation measurement data is present on separate Excel spreadsheet tabs. The “Results” information links the summary of the project verification status.

Nicolas explained, “Key measurement data from the individual macros are represented in different Excel tabs. This simulation measurement data can range from simple scalar values to a vector of measurements associated with parameter values from sweeps or Monte Carlo sampling. The Results tab in the Excel spreadsheet contains the references to individual cells among the tabs. Any additional Excel calculations or complex expressions can be added to quickly summarize the overall Pass/Fail status of each IP specification.”

“Why Excel?”, I asked.

“We chose to interface the Tanner Designer dashboard to Excel for simplicity, familiarity, and efficiency. The interface is seamless. When simulations are rerun, an ‘Update’ command automatically re-loads the Tanner Designer project database and the related Excel spreadsheet with the new simulation measures, and re-calculates formulas/expressions for the current status of specification checks.”, Nicolas replied.

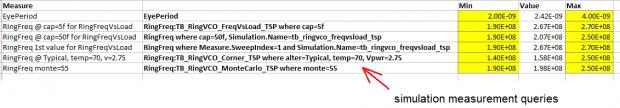

He added,“And, we developed a simple query language for analog designers to describe the specific database information to place into the dashboard and Excel tab spreadsheet.” Examples of database queries are shown below.

There are data links from Excel back to Tanner Designer to complete the project management loop. The Excel Results tab information is reflected back to the dashboard, to serve as the single (high-level) project management status view.

There are “hot links” from Excel to Tanner Designer, as well — if a measurement specification created in the Results tab is not correctly populated after an update, there is a highlighted notification in the dashboard.

Tanner Designer can also embed more complex data, such as detailed simulation waveforms, and (especially) graphs/charts generated by Excel — see the figure below for an example.

Building upon the extensive capabilities in Excel to leverage ‘templates’, Tanner Designer can also serve as a very efficient means to generate IP block datasheets, for internal design reviews and/or external documentation.

The analog IP designer typically wears many hats, with verification lead and project manager responsibilities among them. There has typically been little focus on tools and flows to assist with the PM tasks, or to establish a formal and consistent methodology for defining and reporting project status and specification pass/fall results. Mentor’s Tanner Designer is a significant step forward to address this requirement.

For more info on Tanner Designer, please follow this link. There is an excellent Webinar with an introduction to Tanner Designer — here’s a direct link.

-chipguy

Share this post via:

Comments

0 Replies to “Project Management Tools for Analog IP Verification”

You must register or log in to view/post comments.