Workshops are a great where to learn hands-on about IC design technology. Mentor has a free workshop to introduce you to creating, simulating and verifying mixed-signal (Analog and Digital) designs.

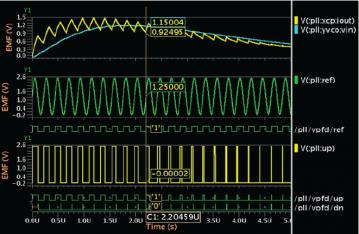

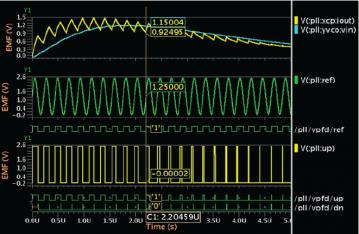

PLL waveforms showing both digital and analog signals.

Dates in Fremont, California

July 26, 2011

September 15, 2011

November 8, 2011

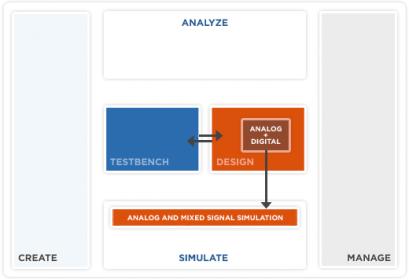

Their tool is called Questa ADMS and spans both digital design with HDL and analog design using SPICE or Fast SPICE.

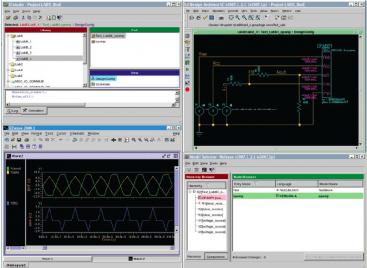

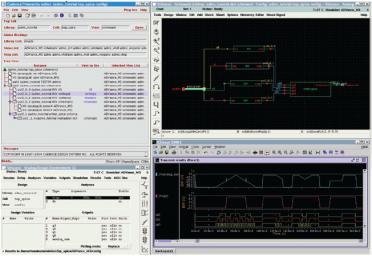

These tools work both in a Mentor environment and the Cadence environment.

Questa ADMS inside Design Architect IC

Questa ADMS inside of the Cadence Virtuoso Analog Design Environment

Overview

Mentor Graphics cordially invites you to attend a FREE “hands-on” Mixed-Signal Design and Verification Workshop. In this workshop we will explore the current trends of IC design and highlight the challenges these trends create. This workshop will expose you to comprehensive solutions necessary to improve your design and verification productivity.

During this lab-intensive technical workshop, you will gain first-hand experience evaluating Questa ADMS, Mentor’s Mixed-Signal Simulation Solution.

Lab 1 – Getting started with ADMS

- Explore the ADMS graphical interface and infrastructure

- Run digital and mixed-signal simulations with an adder and ADC circuits

Lab 2 – Mixed-Signal Simulation: Digital-centric

- Learn about using analog SPICE circuits within a digital netlist hierarchy

- Explore the analog-digital interface and how to bridge the domains

- Understand the importance of validating analog and digital blocks together

Lab 3 – Mixed-Signal Simulation: Analog-centric

- Learn how to use HDL behavioral models within a schematic

- Observe the impact of AMS modeling on performance and functionality on a PLL circuit

Comments

0 Replies to “Want to learn Mixed-Signal Design and Verification?”

You must register or log in to view/post comments.