Last week I met with Joseph Davis, Ph.D. at Mentor Graphics in Wilsonville, Oregon to learn about a new product designed for full-custom IC layout designers to improve productivity.

The traditional flow for full-custom IC layout designers has been nearly unchanged for decades:

- Read a schematic or use Schematic Driven Layout (SDL)

- Create an IC layout with polygons, objects, generators or cells

- Manually interconnect or use a P&R tool

- Run DRC and LVS in batch

- Find and fix errors

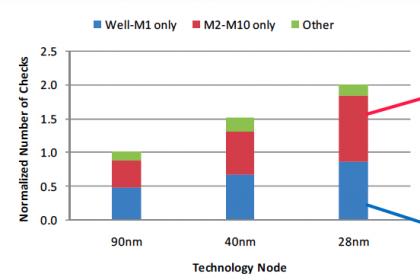

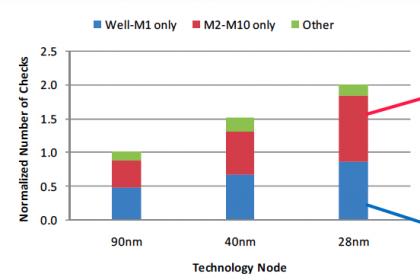

As designers use the newest layout nodes at 28nm the complexity explosion in DRC rules has been quite daunting with a doubling of rules compared to 90nm:

IC layout designers cannot keep all of these new rules in their head while doing custom layout and running DRC tools in batch mode dozens or hundreds of times a day will certainly slow down design productivity.

Faced with these pressures of more DRC rules and increased difficulty to get a clean layout a design team could choose several options:

[LIST=1]

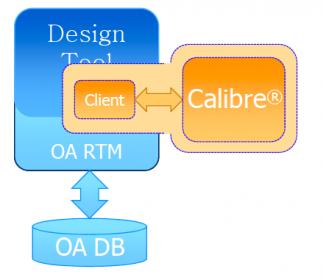

None of these options looks appealing to me, so it was good news to hear about a new approach to make the life of IC layout design go faster. This approach is to use the Calibre tool interactively while doing IC layout instead of using it in batch mode:

The demo that I saw was a custom IC layout at 28nm with dozens of transistors, 6,649 shapes and about 3,000 checks. When this layout was run with Calibre in batch mode it took about 20 seconds to produce results, however when used interactively the results came back in under 1 second. Both runs used identical rule decks for Calibre, and were run on the same CPU, the difference being that the interactive version of Calibre produced near instant results.

Mentor calls this new tool Calibre RealTime and it works in a flow that uses the Open Access database, a de-facto industry standard. It was a bit odd to be inside of a Mentor building and watch a demo using the SpringSoft Laker tool for IC layout since it competes with IC Station from Mentor. You can get this same technology for Mentor’s IC Station tool but you have to wait until July.

Benefits of this interactive approach with Calibre RealTime are:

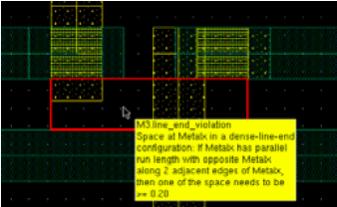

- I can see my DRC errors rapidly, just mouse over the error region and read a detailed description of my DRC violations.

- The DRC rule deck is the full Calibre deck, so I’m getting sign-off quality results at the earliest possible time. In the past IC tools had some rudimentary interactive DRC checks however they were never sign-off quality, so you still had to run a batch DRC run only to discover that you had lot of fixes still required.

- With the SpringSoft Laker tool I just push one button and get Calibre results in under a second. There’s no real learning curve, it’s just that simple to install and start using immediately.

- Of course I wouldn’t run this interactive DRC check on a design with more than 1,000 transistors at a time, it’s really meant for smaller blocks. If you use Calibre RealTime while your design is being created on small blocks, then it’s going to catch your DRC errors almost instantly so you can start fixing the layout and avoiding making the same mistake again.

- Mentor IC Station users will benefit from this same productivity boost in just a few months, so you should be able to see a demo at DAC.

- Works with MCells, PCells, routers andmanual editing. So it fits into your IC flow at every step of the process.

Summary

The Calibre RealTime tool will certainly save you time on full-custom IC layout by producing DRC results in under a second on small blocks. SpringSoft Laker users will benefit first, then IC Station users in a few months.

It makes sense for Mentor tools to work with the Open Access database, now I wonder if IC Station will be the next tool to use OA?

Share this post via:

Comments

0 Replies to “Getting Real Time Calibre DRC Results”

You must register or log in to view/post comments.