The goal of SoC design teams is to tape-out their project and receive working silicon on the first try, without discovering any bugs in silicon. To achieve this lofty goal requires all types of specialized checking and verification during the design phase to prevent bugs. There are checks at the system level, RTL level, gate level,… Read More

Tag: drc/lvs

SIP Modules Solve Numerous Scaling Problems – But Introduce New Issues

Multi-chip modules are now more important than ever, even though the basic concept has been around for decades. With The effects of Moore’s Law and other factors such as yield, power, and process choices, reasons for dividing what once would have been a single SOC into multiple die and integrating them in a single module have become… Read More

Empyrean Technology‘s Complete Design Solution for PMIC

Power management integrated circuits (PMICs) are integrated circuits for power management. Driven by the strong demand in consumer electronics, IoT, and the automobile industry, the design for PMIC is getting more challenging in terms of integration, reliability and efficiency. The design methodology needs to be updated… Read More

Viewing the Largest IC Layout Files Quickly

The old adage, “Time is money”, certainly rings true today for IC designers, so the entire EDA industry has focused on this challenging goal of making tools that help speed up design and physical verification tasks like DRC (Design Rule Checks) and LVS (Layout Versus Schematic). Sure, the big three EDA vendors have… Read More

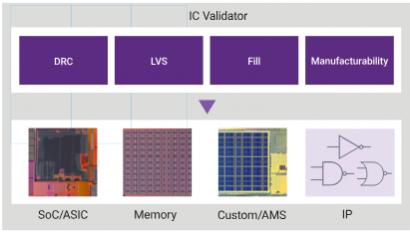

Physical Verification with IC Validator

If a picture worths a thousand words, a tapeout quality SoC design with billions of polygons would compose a good book. To proofread this final design transformation format requires a foundry driven DRC/LVS signoff solution that nowadays is becoming more complex with further process scaling and shrinking pitch dimension.

Despite… Read More

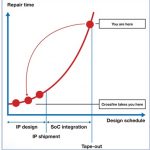

Crossfire Baseline Checks for Clean IP at TSMC OIP

IP must be properly qualified before attempting to use them in any IC design flow. One cannot wait to catch issues further down the chip design cycle. Waiting for issues to appear during design verification poses extremely high risks, including schedule slippage. For example, connection errors in transistor bulk terminals where… Read More

IC Layout with Interactive or Batch DRC and LVS Results

IC designers have a long tradition of mixing and matching EDA tools from multiple vendors, mostly because they enjoy best-in-class tools, or they just purchased each EDA tool at a different time and asked for them to work together. Such is this case with IC layout tools from Silvacoand DRC/LVS tools from Mentor Graphics. Pawan Fangaria… Read More

Getting Real Time Calibre DRC Results

Last week I met with Joseph Davis, Ph.D. at Mentor Graphics in Wilsonville, Oregon to learn about a new product designed for full-custom IC layout designers to improve productivity.

The traditional flow for full-custom IC layout designers has been nearly unchanged for decades:

- Read a schematic or use Schematic Driven Layout