Multiple, independent clocks are quintessential in SoCs and other complex ASICs today. In some cases, such as in large communications processors, clock domains may number in the hundreds. Clock domain crossings pose a growing challenge to chip designers, and constitute a major source of design errors–errors that can easily slip past conventional verification tools and make their way into silicon.

When these errors make it into silicon, the costs are high. A single silicon re-spin may cost $10 million and extend time-to-market by months, greatly reducing the chip’s market share and profit potential.

Therefore, there is a substantial benefit to identifying and correcting CDC problems in the early stages of the design, at the RTL level, when corrections may be made quickly and at minimal cost. Unfortunately, cycle-based simulation, the mainstay of RTL-stage verification, is not well suited to finding and tracing timing-related errors resulting from CDC problems. Static timing analysis tools treat clock domain crossings as exceptions and ignore them. Furthermore, traditional structural CDC analysis tools can help identify clock domain crossings and perform some basic synchronization checking, but none offers the kind of comprehensiveness or precision users require. Such tools tend to simultaneously overlook a number of real design errors and over-report a large numbers of false violations.

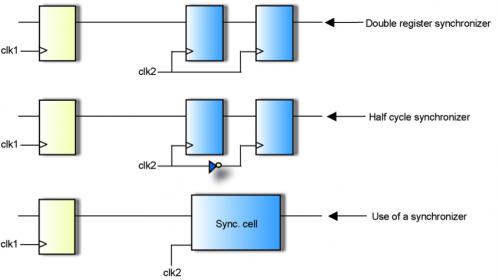

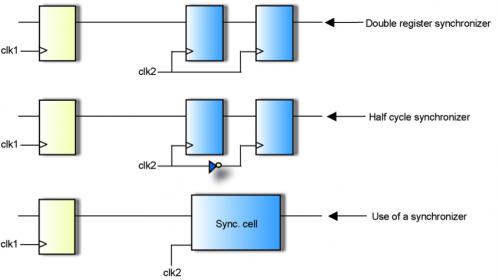

Control signal synchronization

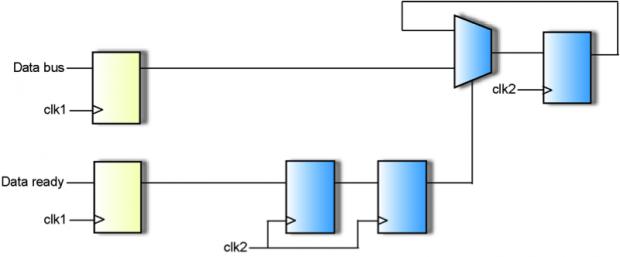

Data signal synchronization

When signals cross from one clock domain to another asynchronous domain, several problems can result:

[LIST=1]

To detect these problems (and ignore non-problem false errors) a good CDC verification tool must:

[LIST=1]

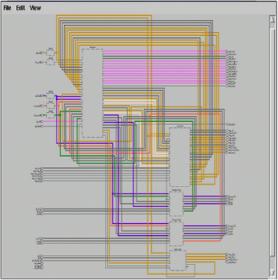

Analysis and display of clock domains

Images: courtesy Atrenta

For more details: the Atrenta CDC white-paper

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?