Verification is always a top priority for any chip project. Re-spins result in lost time-to-market and significant cost overruns. Chip bugs that make it to the field present another level of lost revenue, lost brand confidence and potential costly litigation. If the design is part of the avionics or control for an aircraft, the… Read More

Tag: clock domain crossing

Automating Reset Domain Crossing (RDC) Verification with Advanced Data Analytics

The complexity of System-on-Chip (SoC) designs continues to rise at an accelerated rate, with design complexity doubling approximately every two years. This increasing complexity makes verification a more difficult and time-consuming task for design engineers. Among the key verification challenges is managing reset domain… Read More

NoCs give architects flexibility in system-in RISC-V design

RISC-V tends to generate excitement over the possibilities for the processor core, any custom instruction extensions, and its attached memory subsystem. Those are all necessary steps to obtaining system-level performance. But is that attention sufficient? Architects who have ventured into larger system-on-chip (SoC) … Read More

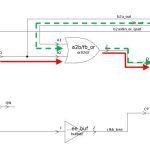

Up front phases improve CDC analysis

Many tools find clock domain crossings (CDCs) in FPGA designs. Some don’t find the right ones since they don’t comprehend things like in-house synchronizer constructs. Some find too many based on misunderstanding intent, inaccurate constraints, and other factors that lead to noise.… Read More

Dominating FPGA clock domains and CDCs

Multiple clock domains in FPGAs have simplified some aspects of designs, allowing effective partitioning of logic. As FPGA architectures get more flexible in how clock domains, regions, or networks are available, the probability of signals crossing clock domains has gone way up.… Read More

An Approach to Clock Domain Crossing for SoC Designs

Blogger Pawan Fangaria wrote about Clock Domain Crossing(CDC) a few weeks ago, and so I followed up tonight and watched a webinarabout CDC presented by Ravindra Anejaof Atrenta. An RTL design engineer would ultimately want a CDC verification tool that offers:

- Fast throughput and thoroughness

- Ability to debug and fix the source

Hierarchical Clock Domain Crossing

One of the first blogs I wrote on SemiWiki was on clock domain crossing (CDC). I thought it was rather a specialized subject, a sort of minority interest. It turned out to be one of the most-read blogs I’ve written. Modern SoCs have lots of unrelated clocks, maybe hundreds, and so ensuring that signals going from one clock domain… Read More

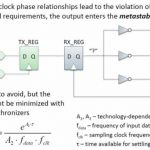

The never-ending quest to kill metastability

The difficulty of an engineering problem can be gauged by two things:

1) The number of attempts to generate a solution.

2) The degree of hyperbole used to describe the effectiveness of the latest solution.

The problem many folks in the EDA industry are after right now is clock domain crossings (CDCs) and the resulting metastability… Read More

Clock Domain Crossing, a potted history

Yesterday I talked to Shaker Sarwary, the senior product director for Atrenta’s clock-domain crossing (CDC) product SpyGlass-CDC. I asked him how it came about. The product was originally started nearly 8 years ago, around the time Atrenta itself got going. Shaker got involved about 5 years ago.

Originally this was a small… Read More

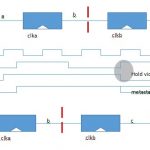

Clock Domain Crossing (CDC) Verification

Multiple, independent clocks are quintessential in SoCs and other complex ASICs today. In some cases, such as in large communications processors, clock domains may number in the hundreds. Clock domain crossings pose a growing challenge to chip designers, and constitute a major source of design errors–errors that can… Read More