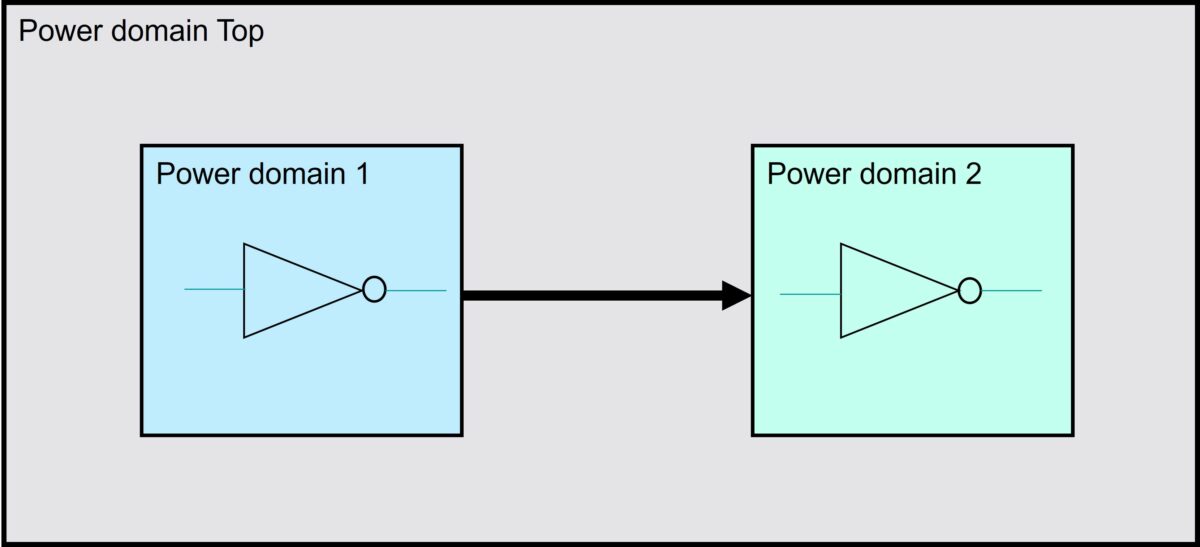

In the realm of mixed signal design for integrated circuits (ICs), level shifters play a critical role for interfacing circuits that operate at different voltage levels. A level shifter converts signal from one voltage level to another, ensuring compatibility between components. Figure 1 illustrates a missing level shifter between power domains.

It’s not uncommon for a member of the design team to miss a level shifter while designing a largeIC. . Although a seemingly obvious mistake, there are a plethora of pragmatic factors that may contribute towards a mistake like this in a large complex design. Some are them are assumption of voltage levels, lack of documentation of specifications, time constraints, complexity of design, inexperienced designers, inadequate simulation and testing and using a previous design as reference.

Depending upon the design team and company size, and the time constraints and resources available for a particular project, one or more of these checkpoints may or may not be available. If absent, the likelihood of design mistakes to inadvertently slip through before fabrication significantly increases.

The difficulty of accurately identifying the need for a missing level shifter, despite all kinds of checkpoints, presents an opportunity for the electronic design automation (EDA) industry to provide a more robust solution that can avoid these all too common human mistakes.

Consequences of a missing level shifter

A missing level shifter in an IC design can have profound consequences that may completely compromise the integrity, performance and even power consumption of the design. Some examples of the consequences that may occurs due to missing level shifter somewhere in the design are:

- Signal integrity issues

- Damage to devices

- Increased power consumption/leakage

- Reduce performance

- Compatibility issues

- Noise sensitivity

Figure 2 shows a diagram of an IP with two power domains. When both power domains are powered-up and the voltage difference between the power domains is less than a threshold value (which you can set in the simulator), there are no issues in the design. However, if the voltage difference is greater than the threshold value, let us say Power domain 2 is operating at a higher-voltage level than Power domain 1, then a logic ‘1’ at Power domain 1 can be assumed a logic ‘0’ at Power domain 2. This leads to incorrect data transmission.

An optimal solution for identifying inter-domain power leakage

The first step towards finding an inter-domain power leakage is finding all DC paths between all power domains. This step is immensely helpful and will list out all possible combinations of DC paths possible between two or more power domains. This step finds every single combination of paths that may exist between two or more power domains. Fortunately, this first step of finding all DC paths is relatively easy.

After finding all DC paths and identify crossings between different power domains, the tool performs a sophisticated evaluation to determine whether these crossings actually require level shifters. This complex analysis demands a comprehensive understanding of the circuit’s architecture and power domain interactions.

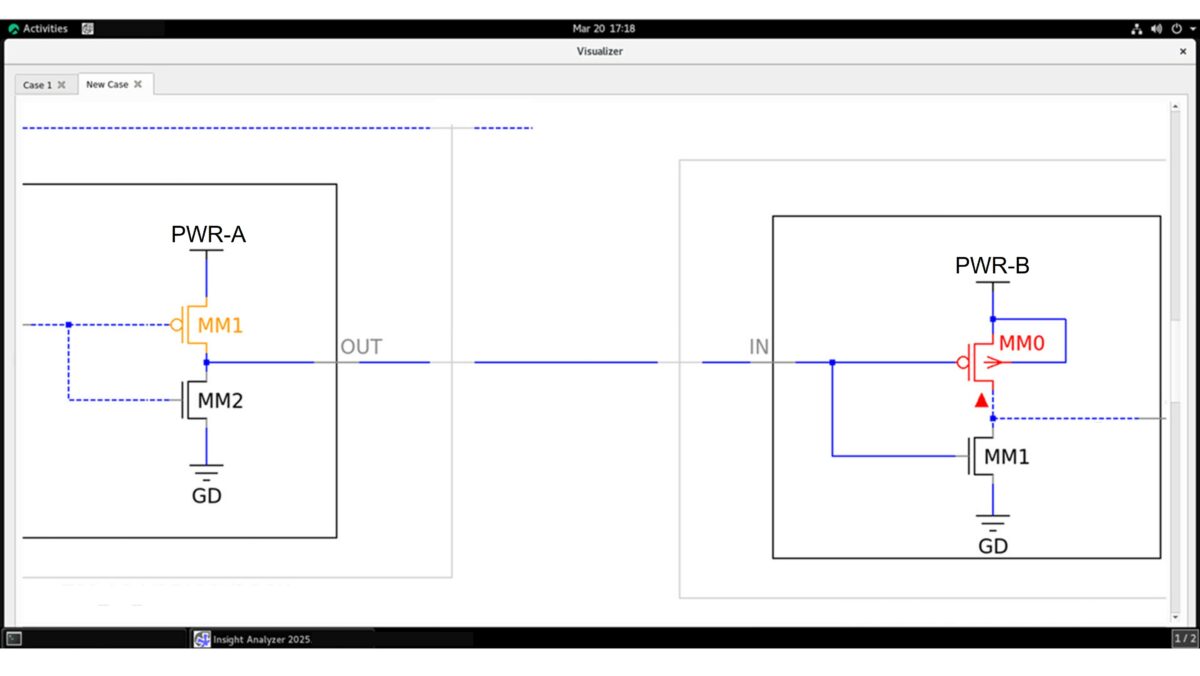

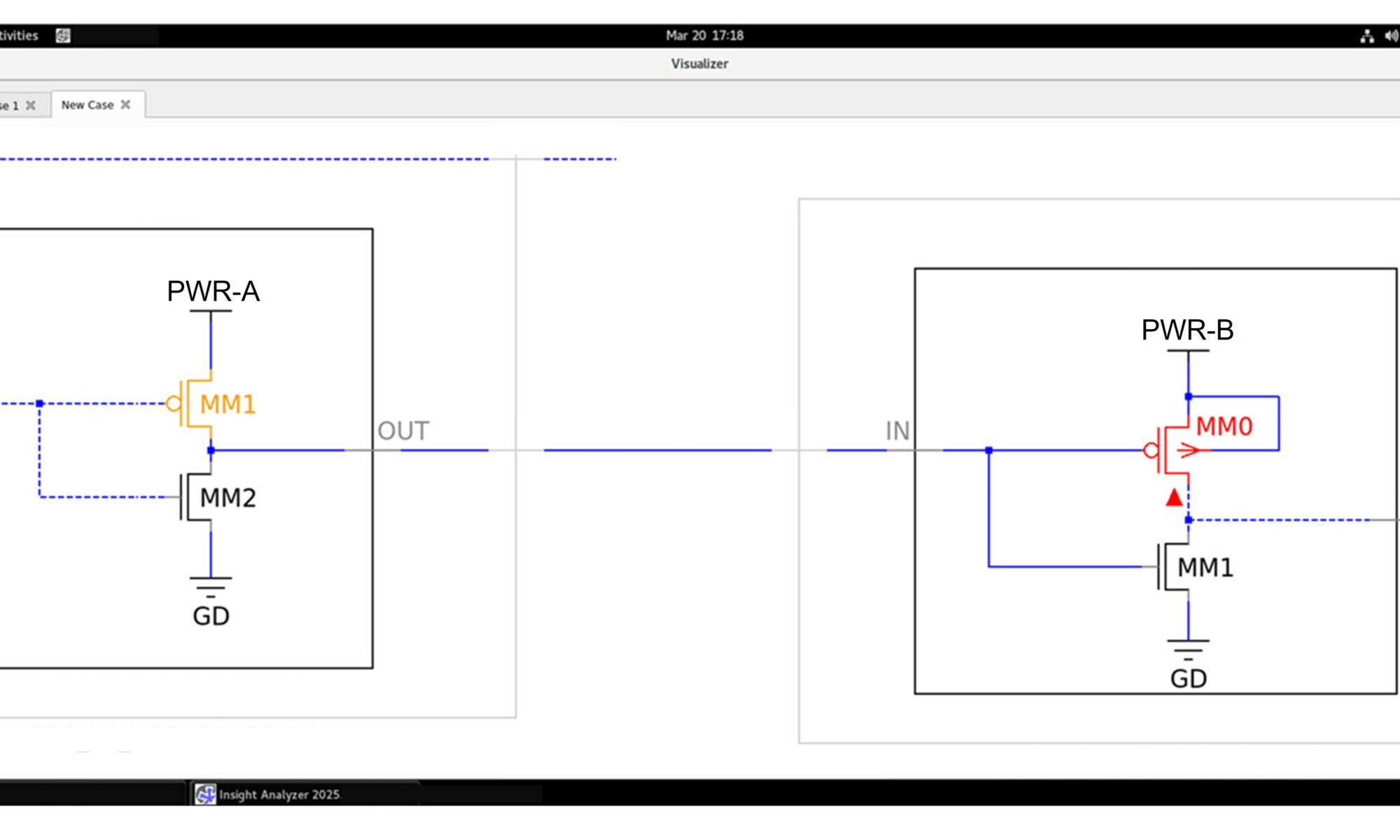

The determination of missing level shifters requires detailed voltage analysis that can only be accomplished through advanced EDA tools. These tools examine critical voltage relationships, specifically the gate-to-source voltage in PMOS devices and gate-to-drain voltage in NMOS devices. The measured voltages are compared against expected values, which are derived from the respective power and ground rail specifications for each domain. When these voltages deviate from expected values, it signals a potential requirement for level shifting.

Siemens EDA offers an innovative tool called Insight Analyzer that can quickly and accurately identify the risk of missing level shifters between power domains, as well as many other circuit reliability issues that are not easily identified using simulation or traditional electrical rule checking tools. Insight Analyzer uses a form of state-based analysis at the pre-layout stage without the need for simulation, so designers can perform early design analysis during the development process. This early, shift-left, analysis makes the design process more efficient, saving time and money.

Conclusion

As semiconductor technology reaches new heights and chip designs are becoming more complicated, with multiple power domains and multiple power states, the risk of missing a level shifter by the designer becomes all too real. The risk of not catching these design elements until much later in the design phase or even post fabrication is at all-time high, with there always being a complicated sets of instances and circumstances which may lead to designer missing a level shifter in the early design phase. The Insight Analyzer tool provides circuit designers with a designer- driven reliability verification flow, capable of running full-chip, transistor-level circuit analysis. Using Insight Analyzer enables circuit designers to improve their design reliability in today’s fast paced environment. You can learn more in my new technical paper Finding missing level shifters between power domains with Insight Analyzer.

About the author, Bhanu Pandey

Bhanu Pandey is a product engineer for Calibre Design Solutions at Siemens Digital Industries Software, with responsibility for the Insight Analyzer circuit reliability analysis tool. His focus and technical experience are in analog circuits. Prior to joining Siemens, Bhanu worked as an analog design engineer. He received his Master of Science degree in Electrical and computer Engineering from Georgia Institute of Technology.

Also Read:

Metal fill extraction: Breaking the speed-accuracy tradeoff

Siemens Describes its System-Level Prototyping and Planning Cockpit

Verifying Leakage Across Power Domains

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.