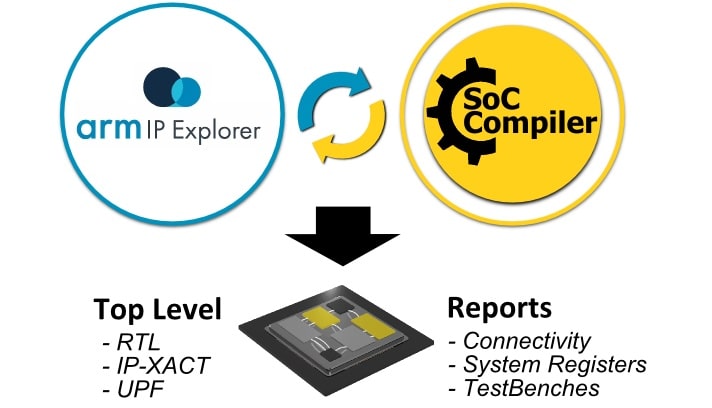

At #61DAC I stopped by the Defacto Technologies exhibit and talked with Chouki Aktouf, President and CEO, to find out what’s new in 2024. ARM and Defacto have a joint SoC design flow by using the Arm IP Explorer tool along with Defacto’s SoC compiler, which helps to quickly create your top-level RTL, IP-XACT and UPF files. This tool flow enables an engineer to define an Arm-based system architecture by selecting from various IP cores from a catalog, then parameterize the core. Adding custom IP blocks complete the system design.

This more automated approach saves many weeks of manual effort, where making changes and updating files is now simplified.

Using Defacto tools like SoC Compiler your team can also configure SoC designs with RISC-V cores. Large chip assembly time can be up to 30X faster by using Defacto. CAD groups can control the SoC Compiler tool with their favorite scripting languages:

- Python

- Tcl

- Java

- Ruby

- C++

I learned that Defacto presented a poster session at DAC, “New SoC Creation Flow based on Extraction and Recreating from Previous SoC”. There are AI customers using SoC Compiler, but I cannot mention any names yet, so stay tuned.

During RTL DFT signoff, there are checks for testability and test coverage evaluation, so that you find any test related issues early in the design cycle when coding RTL. You can even explore moving test points around and see the impact on implementation. Designers can also simulate their peak power during RTL, instead of waiting for gate-level implementation, saving time and providing critical feedback.

With a general shortage of SoC engineers, using automation from EDA tools like SoC Compiler is another way to keep projects on schedule.

Chouki told me that their EDA spinout, Innova, has a tool to predict how many EDA licenses and compute resources will be required for any SoC project. The Innova PDM has an AI engine and is being used first in Europe with initial customers and will soon expand to more geographic regions. The whole idea with Innova PDM is to reduce project costs by better planning metrics.

Summary

At SemiWiki we’ve been blogging about Defacto since 2016 and every year they continue to steadily add new EDA tool features and growing their spinout company Innova. The biggest news for 2024 has to be the joint design flow with Arm and being included in the partner ecosystem catalog. The enthusiasm of talking with Chouki Aktouf is simply contagious and brings a smile to my face, so plan to give this company a look and follow up with a visit or call.

You can find Defacto at shows like DAC, IP-SoC, ITC, ChipEx.

Related Blogs

- Defacto at the 2024 Design Automation Conference

- Innova at the 2024 Design Automation Conference

- WEBINAR: Joint Pre synthesis RTL & Power Intent Assembly flow for Large System on Chips and Subsystems

- Lowering the DFT Cost for Large SoCs with a Novel Test Point Exploration & Implementation Methodology

- Defacto Celebrates 20th Anniversary @ DAC 2023!

Comments

There are no comments yet.

You must register or log in to view/post comments.