In the relentless pursuit of ever-increasing data speeds, the 1.6 Terabits per second (Tbps) era looms on the horizon, promising unprecedented levels of connectivity and bandwidth within data centers. As data-intensive applications proliferate and the demand for real-time processing escalates, the need for robust and efficient communication infrastructure becomes paramount. At the heart of this infrastructure lie electro-optical interconnects, poised to revolutionize data transmission with their blend of high-speed, low-latency, and power-efficient capabilities. The adoption of 224G serial links emerges as a critical enabler for achieving end-to-end 1.6Tbps traffic capacity. These high-speed serial links serve as the backbone of data transmission, facilitating seamless communication between various components within the network. Their ability to handle ultra-high data rates and bandwidth demands makes them indispensable for the realization of next-generation communication systems. As with every major technology advancement, there are inherent challenges to be overcome. Both the optical channel and optical engine introduce nonlinear behavior. Traditional simulation-assisted design methods often model optical engines using electrical circuit languages and simulators, assuming linear channels, leading to overly optimistic assessments of interconnect performance.

At the recently held DesignCon 2024 conference, Synopsys presented the results from their electrical-optical co-simulation study using native electrical and optical signal representations. A highlight of this study is that the system design methodology that was utilized accounts for both linear and non-linear impairments, agnostic of technology, data rate, and modulation format. The “System design methodology, simulation and silicon validation of a 224Gbps Serial Link” paper submission received DesignCon 2024 Best Paper Award.

The following are some excerpts from Synopsys’ two paper submissions at DesignCon, namely, “Performance assessment for high-speed 112G/224G SerDes with Direct-Drive Optical Engine” and “System Design Methodology, simulation and silicon validation of a 224Gbps serial link.”

Forward Error Correction in the 1.6T Era

Forward Error Correction (FEC) mechanisms play a pivotal role in enhancing the reliability of data transmission over high-speed links, particularly in the context of 1.6Tbps traffic. While FEC helps combat errors and ensures data integrity, its implementation introduces additional considerations such as power consumption and latency. Striking the right balance between Bit Error Rate (BER), power efficiency, and latency becomes imperative in designing efficient communication systems for the 1.6T era.

The Emergence of Electro-Optical Interfaces

To meet the evolving demands of the 1.6Tbps era, electro-optical interfaces are poised to play a transformative role. These interfaces leverage the advantages of optical technology to deliver high-speed, low-latency, and power-efficient communication solutions. Technologies such as Co-packaged Optics (CPO) and Die-to-Die (D2D) interconnects offer promising avenues for seamlessly integrating optical components into existing data center architectures, ushering in a new era of efficiency and performance.

Navigating Impairments in End-to-End Links

However, the deployment of end-to-end 224G links is not without its challenges. The conventional approach to simulating optical interconnects using electrical circuit languages and simulators, while effective in some cases, comes with several tradeoffs. Impairments such as noise, jitter, distortion, and crosstalk can significantly degrade signal quality and impact overall performance. To address these challenges, meticulous attention must be paid to modeling and mitigating impairments, ensuring the robustness and reliability of communication infrastructure in the face of non-linear effects inherent in optical and electro-optical interfaces.

The Role of Accurate System Modeling

Accurate system modeling is paramount in navigating the complexities of electro-optical interconnects and countering the non-linear effects inherent in optical transmission. By meticulously simulating various components and their interactions, designers can gain invaluable insights into system behavior and identify potential areas for optimization. Furthermore, correlation with silicon implementation ensures that simulation results closely align with real-world performance, enabling informed decision-making and efficient design iterations.

System Simulation to Silicon Correlation Comparison

In Synopsys’ electro-optical co-simulation study, the process of correlating system simulation with silicon involved a detailed setup for performance characterization in the lab. The setup encompassed various components including a BERT, cables, test board daughter card, and the device under test residing in an Ironwood socket. The s-parameters considered in the system model included responses from the Wildriver, the taconic fastrise 12-layer daughter card, and the testchip package. The comparison between silicon results and system simulation outputs showcased the correlation between the two. Overall, the findings from the study underscored the effectiveness of the system simulation model in capturing silicon behavior and provided valuable insights into system performance and optimization.

The below four charts indicate similarities in the PAM4 levels, EYE opening, and BER performance when simulation and silicon were compared.

![]()

![]()

![]()

![]()

The impulse response comparison below shows a slight difference in the lock point between simulation and silicon but overall correlation in shape.

![]()

The below chart shows the equalization capability of the receiver, with the DSP compensating for ISI and flattening the overall channel response.

![]()

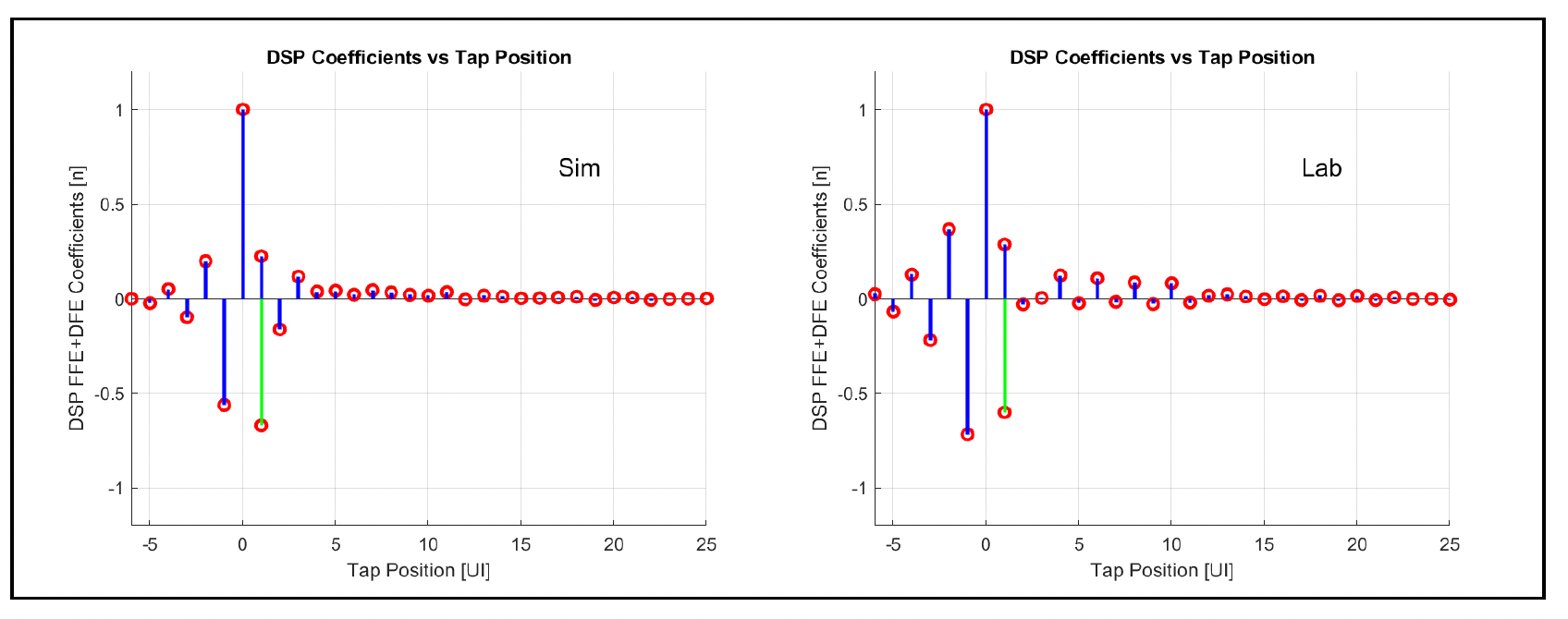

The below chart captures the FFE and DFE coefficients from simulation and silicon readings, indicating some differences attributed to variations in the AFE transfer function and CDR lock point.

Summary

As data centers transition into the 1.6Tbps era, the integration of electro-optical interconnects holds the key to unlocking unprecedented levels of connectivity, bandwidth, and efficiency. Through meticulous system modeling, simulation, and correlation with silicon implementation, designers can harness the full potential of these technologies, ushering in a new era of innovation and performance in data center infrastructure. With the convergence of high-speed serial links, advanced FEC mechanisms, and emerging electro-optical interfaces, data centers are poised to meet the escalating demands of modern computing and networking applications, paving the way for a future of unprecedented connectivity and efficiency.

For more details and access to the full papers presented at DesignCon, please contact Synopsys.

For more information about Synopsys High Speed Ethernet solutions, visit www.synopsys.com/ethernet

Also Read:

Why Did Synopsys Really Acquire Ansys?

Synopsys Geared for Next Era’s Opportunity and Growth

Automated Constraints Promotion Methodology for IP to Complex SoC Designs

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.