Semiconductor IP design re-use has enabled the relentless growth in complexity of SoC and chiplet-based systems over the years, and with IP reuse comes many unique challenges. Fabless design companies use IP provided by a vibrant ecosystem of IP suppliers and foundries, plus internal re-use in the quest to get to market more quickly than starting from a blank slate. Standards organizations Accellera and the IEEE have addressed the challenges of IP design re-use through the IP-XACT standard, dating all the way back to 2004 when IP-XACT 1.0 was released. The latest standard is IEEE 1685-2022, so that’s 18 years of progress and history for IP reuse.

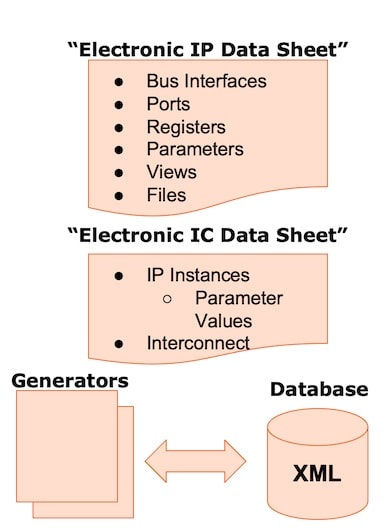

There’s a webinar hosted by Agnisys on October 25th that brings us up to speed on IP-XACT 2022, and the presenter is Devender Pal Khari, a member of the Accellera IP-XACT Working Group. The IP-XACT standard defines how files in XML format describe an IP block so that EDA tools and automated flows can quickly understand essentials, like:

- Ports

- Bus Interfaces

- Registers

- Memory elements

- Connections

- Parameters

- Hierarchy

Source: IP-XACT Tutorial by Accellera at DV Con US 2023 The benefits of using a standard like IP-XACT are that it represents a single specification for all IP information, a single way for registers to be defined, and all needed representations can be generated from a single source using an automated workflow.

New for IP-XACT 2022

The webinar goes into technical detail of all the latest updates to the specification, along with reasons for the changes. The conditional element isPresent has been removed, yet for backward compatibility it is supported through Accellera Vendor Extensions.

Examples are presented on typeDefinitions for memory maps – memoryMapDefinition and memory MapDefinitionRef. They also show how the Tight Generator Interface (TGI) is used to communicate between the design environment and generators.

Power domains used in the Unified Power Format (UPF) are shown with the element componentInstances. Power constraints are support with elements named powerConstraint and powerDomainRef.

User-defined modes are now supported to allow for conditions in dynamic configurations. These modes are then referenced in memory elements, ports, power domains and interfaces. Examples are shown for modes defined on a port, and power domains linked based on modes.

Summary

Agnisys has been focused on EDA automation for HW/SW interfaces since 2007, and are active members of the IP-XACT working group, so they have the expertise to assist SoC designers in using methodologies that support IP reuse.

The webinar from Agnisys on IP-XACT 2022 is October 25th, from 9AM to 9:45AM PDT, and registration is online. Engineers using IP-XACT will benefit from the examples showing what has changed in the latest release, then begin to update their methodology. This is a technical webinar for engineers to further their skills and understanding.

Related Blogs

- WEBINAR: Driving Golden Specification-Based IP/SoC Development

- The Inconvenient Truth of Clock Domain Crossings

- Visit with Agnisys at DAC 2023 in San Francisco July 10-12

- Can We Auto-Generate Complete RTL, SVA, UVM Testbench, C/C++ Driver Code, and Documentation for Entire IP Blocks?

- ISO 26262: Feeling Safe in Your Self-Driving Car

- DAC 2021 – What’s Up with Agnisys and Spec-driven IC Development

- AI for EDA for AI

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era