The ever-increasing demands placed on Intellectual Property (IP) and System-on-Chip (SoC) development teams have resulted in an ever-increasing need for automation solutions that can boost productivity without contributing to further risk. Certainly, demands for automation have long been the drivers behind the growth of the EDA industry, and, in turn, the expansion of the many market segments and application spaces that EDA has come to serve. However, mounting chip complexity, in combination with demanding customers and ever-shrinking market windows, poses its own set of roadblocks to those much-needed automation solutions.

Working closely with so many market makers and leading-edge startups across a wide variety of applications, Agnisys got to see, first-hand, the many challenges being faced by those development teams. This resulted in Agnisys deciding to take aim at specification automation solutions that could address those same challenges. We asked ourselves what could be done to generate the required files for design, software, verification, validation, and documentation for semiconductor development directly from executable specifications.

Due to the ubiquity of registers in chips, and partly to their sheer numbers, Agnisys focused on the automation of register design, verification, programming, validation, and documentation. It was uncommon for a hardware software interface (HSI) to define thousands to millions of registers, with a correspondingly large API to access them. Consequently, the process of manually designing and programming all these registers came to prove daunting.

To eliminate that excessive burden, specification automation just made sense. If you could specify your registers using an unambiguous, executable format, then it would be possible to automatically generate all sorts of files for everyone on your project team. And when the specification changes, as is always the case, the files for each team member can be regenerated to reflect those inevitable changes.

No doubt many of you may have already developed a do-it-yourself (DIY) register automation solution. With standard formats such as SystemRDL, it can certainly seem easy enough to write a script or program to read the specification and generate the register-transfer-level (RTL) design code. But the real-world application of DIY solutions seldom works to plan.

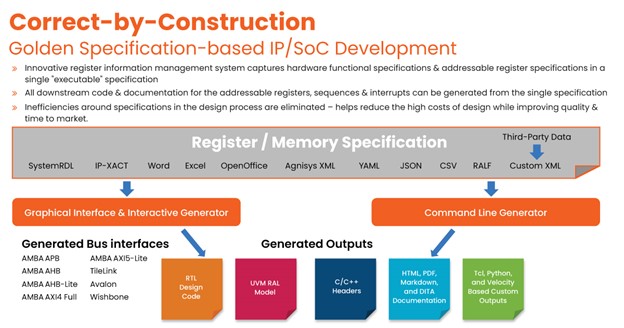

By focusing both certified and standards-compliant specification automation on the problem, much can be done to improve and accelerate productivity. And, with front-end automation advances that encompass an innovative register information management system to capture hardware functionality and an addressable register map in a single “executable” specification, it is now possible for downstream code and documentation for the addressable registers, sequences, and interrupts to be generated from the single specification. Add to this design process the elimination of the inherent specification inefficiencies, and you can not only reduce the high costs of design, but you can also improve quality and time to market.

Taking the wish lists of our customers, we developed specification automation solutions that can quickly and efficiently create correct-by-construction reusable designs. Not only can our user quickly and comprehensively verify registers and memories, but they can also swiftly generate device drivers, as well as automatically generate derived documentation for tech-pubs, lab, internal and external customer.

And in the design process, inefficiencies can be eliminated. Errors can be prevented from entering the system by giving appropriate error messages in the specification itself. Users can carefully manage register information – and any inevitable changes – throughout the design process, thereby increasing productivity for the entire development team with auto generation of register database information delivered in the formats desired by the various teams. Ultimately, design costs are reduced by reducing iterations that are the result of a lack of accurate communication between various teams.

Also Read:

The Inconvenient Truth of Clock Domain Crossings

ISO 26262: Feeling Safe in Your Self-Driving Car

Share this post via:

Siemens U2U 3D IC Design and Verification Panel