Who first came up with this term shift-left ? I’d assumed Siemens EDA as they use it so widely. But their latest white paper on the productivity improvements possible with shift-left Calibre IC verification flows puts the record straight: a software engineer called Larry Smith bagged the naming rights in a 2001 paper (leapfrogging hardware engineers who’ve been doing prototyping for decades).

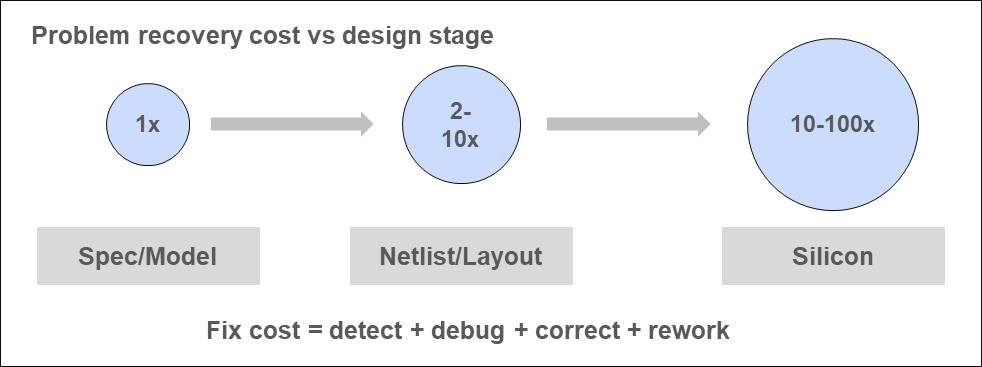

It’s well known that catching problems earlier in the design process can reduce the rework cost by orders of magnitude.

While the detect, debug and correct costs might not vary much through the flow, it’s rework costs that escalate as fixes require longer fixing and verification loops, with potential hardware respins.

Not all design errors and violations are created equal – some have higher impact and fixing costs than others – and design checks fall into two categories: strictly functional (binary; pass/fail) and attribute checks which are qualitative (checked against values) where there may be more scope to over-design earlier or perhaps waiver later.

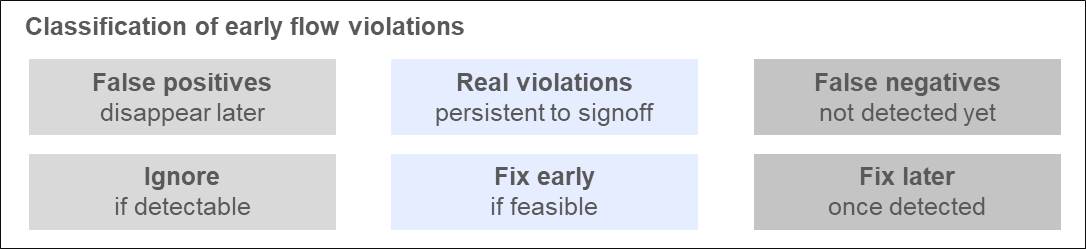

Shift-left strategies hope that early violation detection reliability is as good as the 100% level at signoff. Let’s consider what actually happens.

Differences in verification engines or rule interpretation between early and signoff checks may result in false positive and/or negative violations. So Siemens make a strong point that a shift-left strategy hugely benefits from using the same engine for physical design checks throughout the flow.

But the toughest challenge in handling large, dirty (early stage or incomplete) designs is the sheer volume of violations. Unless we do something smart, the signal to noise ratio here can get pretty bleak. And anyone who’s done much verification will know that huge error and warning reports often cluster into similar types with common causes. Figuring out these patterns often takes time, even with experienced designers.

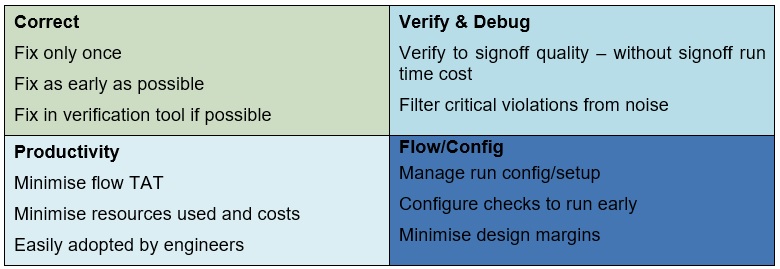

Features we’d like in a shift-left flow might include:

Optimizing shift-left in the Calibre nm Platform flow

How does a Calibre flow measure up to these challenges ?

A Calibre shift-left flow must include the whole range of physical verification checks – LVS, DRC, ERC, PERC, DFM and reliability – as well as design modifications like metal fill and in-design fixing (DRC: Design rule checking; LVS: Layout-vs-schematic; ERC: Electrical rule checking; PERC: Programmable ERC; DFM: Design for manufacturing).

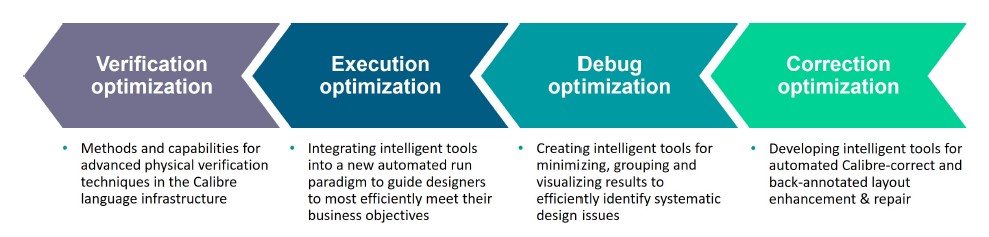

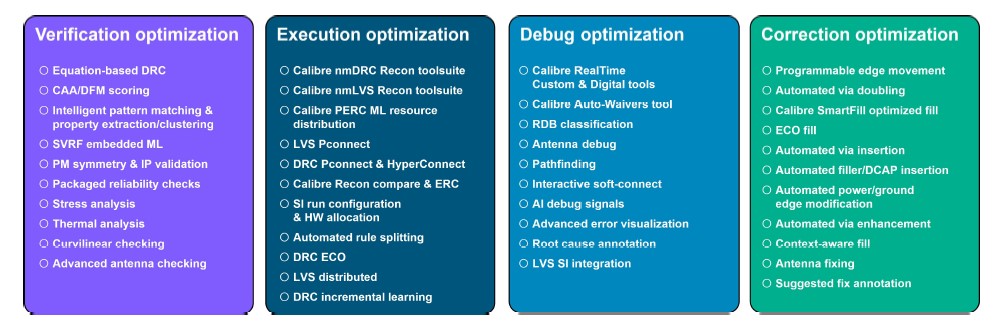

We can’t just optimize the flow without first making sure the tools have the capabilities to do the necessary early design checking. Calibre has added many features here and considers these from four aspects:

Early-stage verification includes equation-based design rule checking, intelligent pattern matching, advanced property extraction and clustering, and embedded machine learning. Reliability is addressed with a set of pre-formatted Calibre PERC™ checks and the Calibre language infrastructure supports signoff verification capability during design and implementation.

Execution optimization covers run configuration and management, including automated run invocation and simplified setup. Calibre nmDRC™ Recon and nmLVS™ Recon tools minimize the rules and data needed for early-stage DRC and LVS verification. Automated check selection and design portioning allows designers to quickly find and fix the real errors while filtering out the irrelevant errors in incomplete designs.

Debug includes color mapping to help minimize and group results and identify root causes quickly, efficiently, and accurately. Intelligent debug signals speed up determining optimal corrections. Calibre RealTime Custom and Digital tools give immediate DRC feedback during design and implementation using standard foundry-qualified Calibre rule decks. Smart automated waiver processing avoids repeating already waivered violations.

Correction is improved with automated, Calibre-correct layout enhancements and repairs that are back-annotated to implementation tool design databases. Calibre’s DFM toolsuite provides a wide range of correct-by-construction layout modifications and optimizations that enhance both manufacturing robustness and design quality. Combining fixing and verification in the same tool also saves license usage and run time.

Another recent Calibre white paper provides a detailed summary around this diagram.

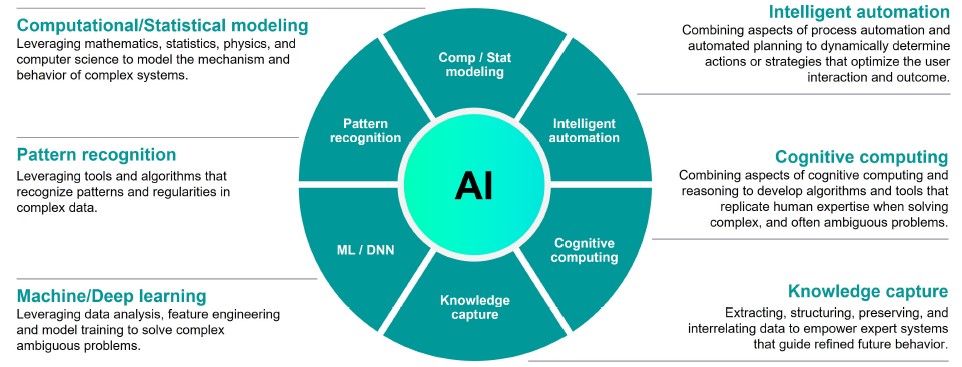

Some of these operations – like smart automation and recognizing patterns in complex result sets – are a natural fit for Artificial Intelligence (AI) techniques, so it’s no surprise to see these are widely used. There’s more detail around the diagram below in the paper.

Summary

Design flows often feel like they were built “tools-up”, with usability aspects added as an afterthought. It’s refreshing to see a more “flow-down” approach here and perhaps no surprise that comes from Siemens as a historically system-centric EDA company.

Much as we’ve seen flows try to consolidate around common timing engines, Siemens argue a strong case for making signoff qualified Calibre PV checks available throughout the design flow.

Siemens have made some really interesting progress with these Calibre shift-left capabilities and clearly see this as a continuing journey with plenty more to come.

Find out more in the original white paper here:

Improve IC designer productivity and design quality with Calibre shift-left solutions; published 3 May 2023

Related Blogs and Podcasts

I found these closely-related white papers very useful:

Michael White, “Optimize your productivity and IC design quality with the right shift left strategy,” Siemens digital Industries Software; published 01 July 2022, updated 10 March 2023.

The four foundational pillars of Calibre shift-left solutions for IC design & implementation flows, published 4 May 2023.

Here’s the original software engineering article introducing the shift-left concept:

Larry Smith, “Shift-Left Testing,” Dr. Dobb’s, Sept 1, 2001.

https://www.drdobbs.com/shiftleft-testing/184404768

Also Read:

Securing PCIe Transaction Layer Packet (TLP) Transfers Against Digital Attacks

Emerging Stronger from the Downturn

Chiplet Modeling and Workflow Standardization Through CDX

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.