Test experts use the acronym BIST for Built In Self Test, it’s the test logic added to an IP block that speeds up the task of testing by creating stimulus and then looking at the output results. Memory IP is a popular category for SoC designers, as modern chips include multiple memory blocks for fast, local data and register storage needs. As the number of memory IP blocks increases in a chip, the challenge is how to implement memory BIST for the minimum area, and maximum throughput. A recent white paper from Harshitha Kodali, Product Engineer at Siemens EDA, focused on this topic, and I’ve learned how a shared bus architecture is the most efficient implementation.

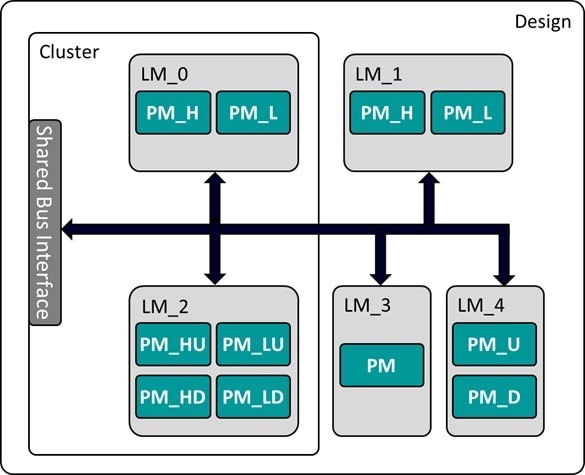

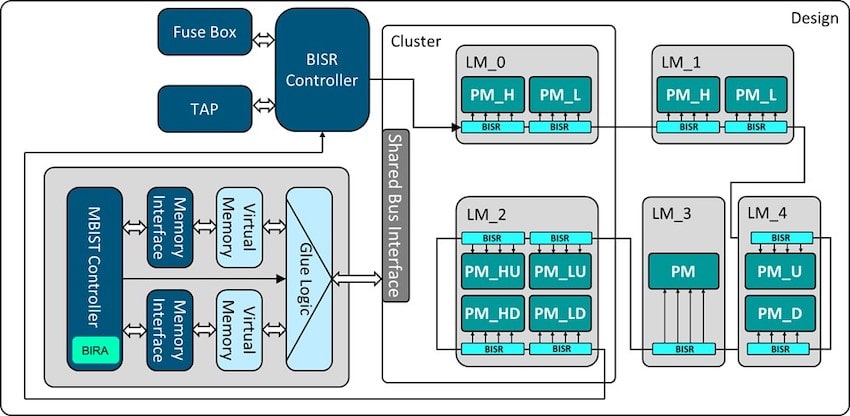

Here’s what a shared bus architecture looks like, where the shared bus is shown in black, physical memories are in teal color, and the physical memories are combined into four logical memories:

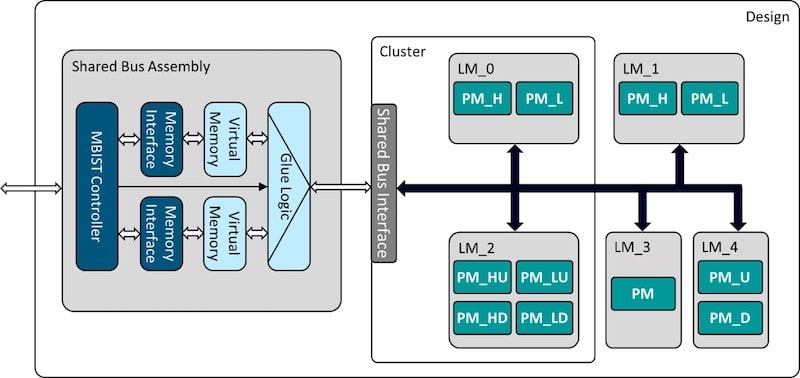

The MBIST logic used to test any of these memories has several components:

Engineers insert this DFT logic automatically at the RTL or gate-level, and they define the memories using a Tessent Core Description (TCD) which has details like:

- Shared bus interface ports

- Access codes per logical memory

- Port mappings between logical memories and shared bus interface

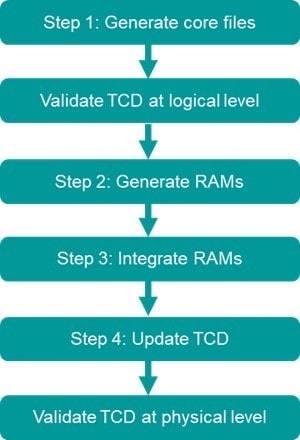

Shared bus learning is a methodology to automatically map the physical memory makeup of every logical memory, and verify that the cluster and logical memory library files are proper. Here’s the flow:

The library validation step ensures that no memory is missed from MBIST testing, port mappings are consistent, and that pipeline stages around the logical memory are consistent with the cluster TCD.

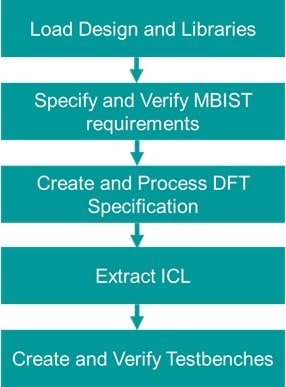

There are five steps to insert the shared bus logic into a design, where ICL is the Instrument Connectivity Language used by a IJTAG flow:

For larger memories the yield can be improved if repairable memories are used, so the Tessent MemoryBIST approach does support this, and inserts the Built-In Repair Analysis (BIRA) plus Built-In Self Repair (BISR) logic. The added BIRA and BISR logic is shown below:

Simple memory instances have a single port for Reading and Writing, however more complex configurations like multi-port and pseudo-vertical stacking are also supported with Tessent MemoryBIST. All of the memory configuration details are defined in the logical memory TCD.

The DFT area overhead can also be optimized if the design has identical memory instances that are not tested concurrently, as the memory interface and virtual memory will be reused.

Summary

Memory BIST with many IP instances can be efficiently implemented with a shared bus test using Tessent MemoryBIST. There’s quite a bit of flexibility in the DFT automation approach offered by Siemens EDA to handle physical memories, logical memories, memory library mapping and validation.

The complete White Paper is available to view online, with a simple registration step, or there’s a recorded webinar online to view.

Related Blogs

- Balancing Test Requirements with SOC Security

- MBIST Power Creates Lurking Danger for SOCs

- Tessent Streaming Scan Network Brings Hierarchical Scan Test into the Modern Age

- Observation Scan Solves ISO 26262 In-System Test Issues

- Mentor Offers Next Generation DFT with Streaming Scan Network

Comments

There are no comments yet.

You must register or log in to view/post comments.