Artificial Intelligence (AI) and Machine Learning (ML) are becoming more and more commonplace in our world. We have Siri, Alexa and Google Assistant that understand our voice commands. Vision systems that recognize objects are used for facial recognition, autonomous driving, medical, geographical and many other applications. The list of applications for AI/ML is growing rapidly, with many of the new applications aimed at modeling complex systems, not just recognition tasks. AI/ML can replace brute force hard-coded approaches with solutions that use relatively sparse data and general purpose algorithms to predict complex behaviors.

That the capabilities of AI/ML can be applied in the field of electronic design has not been lost on researchers and tool developers. EDA is a field where characterization and modeling of complex systems is a continuous requirement. The holy grail of applying AI/ML to electronic design systems is that design operations, such as circuit optimization, placement & routing, etc., could be automated as well. At the very least AI/ML is seen as something that can assist with device and library characterization, and simulation. It has already been used by several vendors to help with high sigma verification and even some DRC operations.

At DAC this year Synopsys was one of the co-sponsors of a panel discussion on the use of AI/ML for electronic design – “Artificial Intelligence Comes to CAD: Where’s the Data?” The panel members were:

Thomas Andersen – Synopsys

Elias Fallon – Cadence

Paul Franzon – NC State University

Raviv Gal – IBM Research Haifa, Israel

Helen Li – Duke University

Sachin Sapatnekar – University of Minnesota

Jiang Hu – Texas A&M University

Xiaoqing Xu – Arm Inc.

The panel discussion focused on two questions: 1) how and when will AI/ML be applied to EDA, and 2) what data will be needed for training and how to get it.

Paul Franzen on the panel said that they have mostly used AI/ML for verification. He sees design as a ripe area, with lots of potential but with many problems that need to be solved. He wants to model high speed IOs, and believes that it could be as accurate as a human made model. He believes that ML can be a useful guide for project teams. There can be a human defined starting point with parameter screening. Then codified human knowledge can be employed. This will help map the design space and can be followed by optimization. We are now in the third wave of AI – deep networks and big data. In the next half of the third wave Paul sees better solving for modeling, improved combination of physics and data, and better feature extraction leading to better data driven modeling. The challenge will be getting useful data with a handful of design examples. Paul says his team uses University generated data and synthetic data.

Raviv Gal reminded us of Mark Twain’s saying that to a man with a hammer, everything looks like a nail. With AI/ML it is important to look for the best methods to solve the various design problems. Raviv is confident that AI/ML is useful for test selection to shorten regression test time. He also says AI/ML based prescriptive analytics could be useful. These could include dashboards or query help. Rule based techniques could help with setting policies for hitting hard to hit coverage events. Formal verification can also benefit from AI/ML based engine and reduction settings. Lastly, he cited value in identifying simulation failures as a known issues or clustering by root causes.

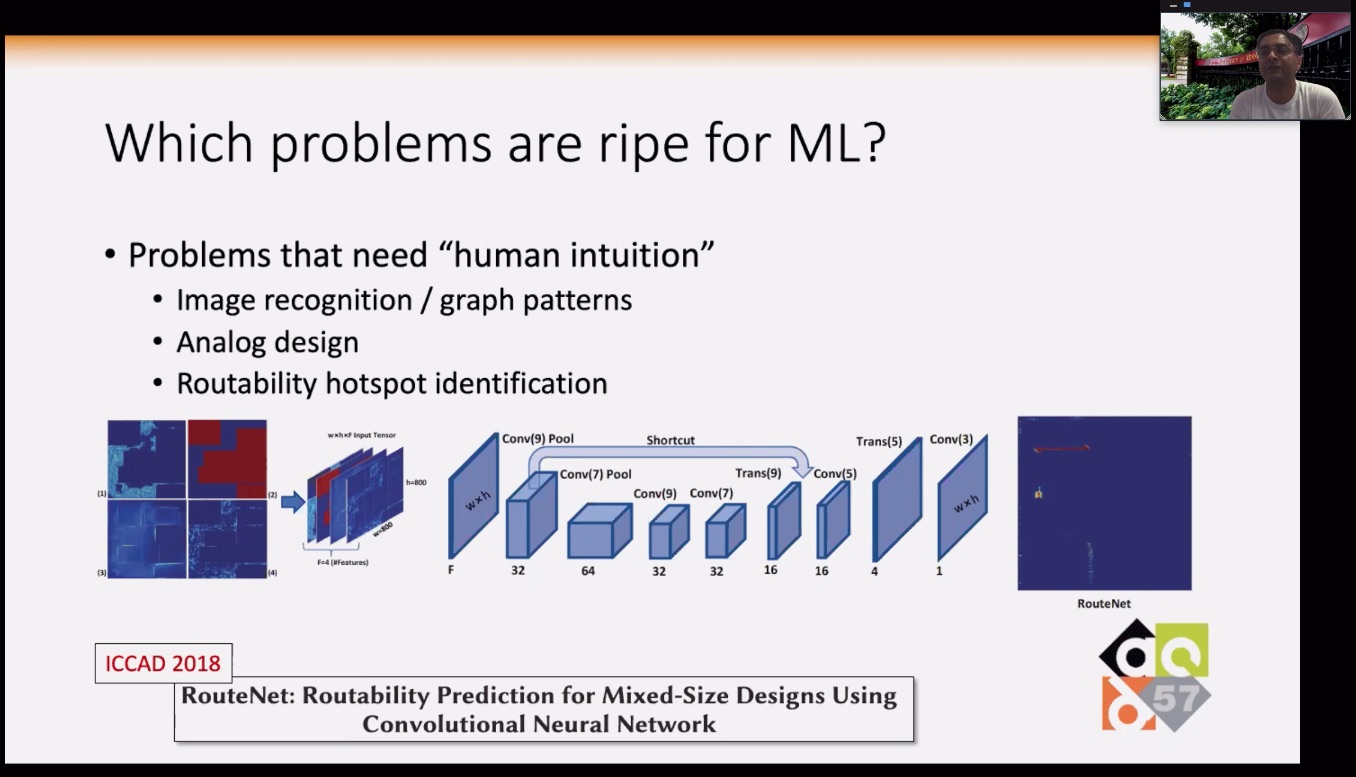

Sachin raised the question that is the big elephant in the room – where do you get the data? Applications that are widely used in the world, such as Netflix movie recommendations are well understood. There is less data available in EDA, and much of it is proprietary. Design houses have lots of data, but EDA vendors do not. Sachin gave one example of the difficulties facing AI/ML in EDA with the problem of having an algorithm identify various implementations of an OTA. Human experts can do this relatively easily, but there are far more difficulties in using AI/ML for this. It requires looking for sub-graph isomorphisms. Sachin asks, how are we going to determine which problems are ripe for AI/ML? He showed an example of using image recognition for detecting areas with routability issues. He also said that a good application could be power grid design. On the topic of training data he points out that old designs might offer too much data actually. The validity of 65nm designs as training for 7nm designs needs to be evaluated. Sachin closed by saying that synthetic data might offer a source of reasonable training data.

There is no doubt that AI/ML will bring big changes to EDA. However, the issues of IP, proprietary data, choosing the best problems to tackle and mode of operation all need to be dealt with over time. Hopefully AI/ML can move from a role in verification to an active place on the design side. As always, EDA tool developers and designers are using the capabilities of current generation hardware/compute systems to develop the next, more complex, generation of systems. The hope is that AI/ML will give us a leg up and help close the gap in design. The panel included a Q&A at the end. Overall it did a good job of highlighting the issues and possible solutions for bring AI/ML into wider use in the area of electronic design.

Also Read:

Hierarchical CDC analysis is possible, with the right tools

What’s New in Verdi? Faster Debug

Design Technology Co-Optimization (DTCO) for sub-5nm Process Nodes

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.