The amount of time spent debugging an SoC dwarfs the actual design time, with many engineering teams saying that debug and verification takes about 7X the effort as the actual design work. So any automation to reduce the amount of time spent in debug and verification would directly impact the product schedule in a big way.

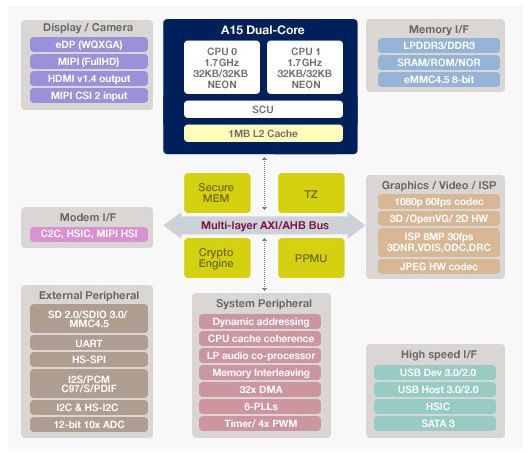

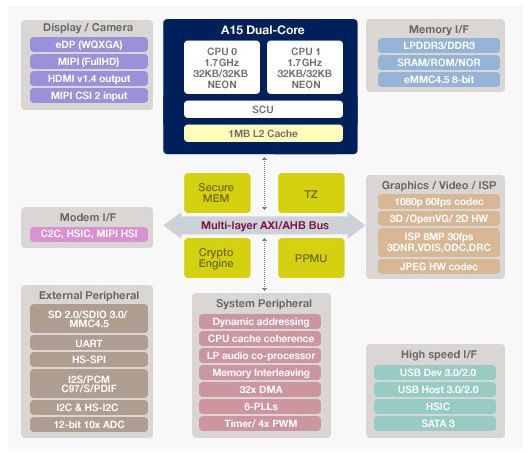

An example Mobile Applications Processor block diagram is shown below and there are a few dozen IP blocks used in this Samsung Exynos 5 Dual along with the popular ARM A15 core.

I’m guessing that a large company like Samsung is likely using IP from third parties along with their own internal IP re-use to get to market quickly.

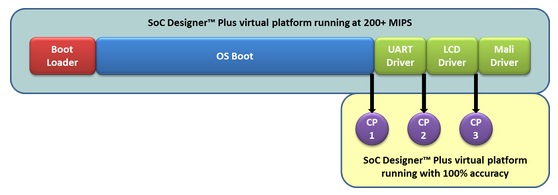

Virtual models can be used during design, debug and verification phases in order to accelerate the simulation speeds. An approach from Carbon Design Systems called Swap & Play allows an engineer to start simulating a virtual prototype with the fastest functional models, and then swap to a cycle-accurate model at some hardware or software breakpoint. So I could simulate a mobile device booting the operating system using fast functional models, and then start debug or analysis using more detailed models at specific breakpoints:

This Swap & Play feature allow the software driver developers to independently code for their IP blocks using the 100% accurate system model without waiting to boot a cycle accurate system. Another benefit is that after the OS is quickly booted you can do performance optimization profiling on your applications or benchmarks.

Carbon Design and ARM developers have collaborated to make this Swap & Play technology work with the latest ARM processor, interconnect and peripheral IP blocks. For Semi IP blocks like fabric and memory controllers that don’t already have a fast functional model, you have several choices:

- Create a SystemC or other high-level model.

- Use a cycle-accurate model, aka Carbonized model. Carbon automatically inserts the adapters needed to go from a Fast Model based system to an accurate model and since most peripherals aren’t big bottlenecks in the actual system, the impact of executing them accurately only when needed is not traditionally a big impact on virtual prototype performance

- Automatically create a fast functional model from a Carbonized model using the SoCDesigner Plus tool.

- Use a memory block. Often you need a place to read and write values.

- Use a traffic generator or consumer model – to look for traffic on the system bus or a sink for traffic.

I see a lot of promise in the third approach because it creates a fast functional model automatically.

For fabric and interconnects the SoCDesigner Plus tool can reduce the logic to a simple memory map, and then create the fast functional model directly from the Carbonized model.

Since memory controllers have configuration registers and other logic which must be modeled, even in the fast functional models, a different approach is needed. Here, SoCDesigner Plus creates a fast functional model which incorporates the Carbonized memory controller to handle configuration accesses which also providing a direct path to memory contents for fast accesses. Since the registers in the memory controller are infrequently changed, using a Carbonized model doesn’t slow down the overall system simulation times much and the vast majority of accesses go directly to memory.

Summary

Using fast, un-timed virtual models is one technique to reduce the debug and verification time on SoC projects. If your SoC design has an ARM core, then consider using the virtual modeling approach from Carbon Design Systems. Bill Neifert blogged about this topic in more detail on July 16th.

Further Reading

- Swap and Play Extended To Chip Fabric and Memory Controllers

- ARM Partners with Carbon on Cortex-A57

- Carbon CEO on Advanced ARM based SoC Design!

- Using Virtual Platforms to Make IP Decisions

lang: en_US

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center