Somehow, when designing a chip it is synthesis and place & route that gets all the attention. But it is no good taping out perfect layout without also having away to test the silicon. Somehow, test just isn’t as glamorous.

Somehow, when designing a chip it is synthesis and place & route that gets all the attention. But it is no good taping out perfect layout without also having away to test the silicon. Somehow, test just isn’t as glamorous.

On September 10-12th is the International Test Conference which, as usual, is at the Disneyland Hotel in Anaheim. I actually went to the conference once when I worked for Virtutech. One use for virtual platforms is making it easy to configure “hardware” and then test the software without actually having to go and find all the boards and cables that would be required to assemble that configuration together in the real world. One of our first customers, Ericsson, used our software in just this way, and reckoned it would take a week to get all the hardware in one place to configure each base station. And a few Disney princesses brighten up any business breakfast.

But ITC is not primarily about software testing, although that is one aspect since so many systems have a large software load. ITC is the world’s premier conference dedicated to the electronic test of devices, boards and systems, covering the complete cycle from design verification, test, diagnosis, failure analysis and back to process and design improvement.

As usual, Mentor has a big presence at ITC. Firstly, they are in booth 211 where you can find out about:

- Hybrid TK/LBIST which combines both compression and logic BIST solutions

- Cell-Aware test for automotive standards such as ISO 26262

- Unique test solutions for ARM processors and embedded memory IP

- 3D test for DRAM and logic

- Hierarchical solutions for large design efficiency and core plug-and-play reuse

- Automated IJTAG support for plug-and-play infrastructure and pattern generation

- Layout-aware diagnosis solutions for understanding and identifying yield loss from test data

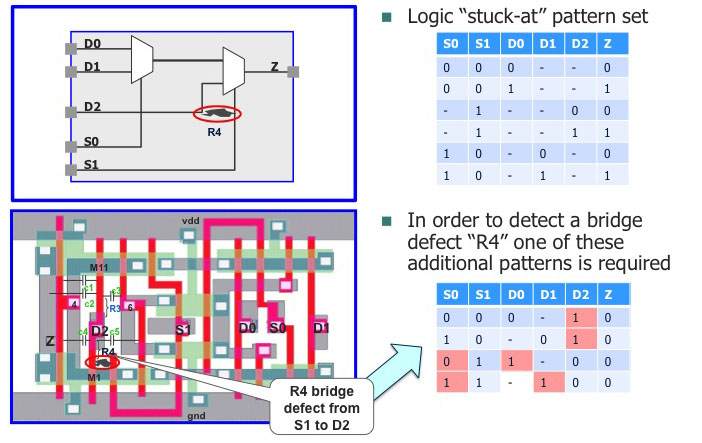

One of the big changes in test where Mentor seems to be taking the lead is making test aware of layout. In the past, IC test has largely used a stuck-at model which has performed amazingly well considering just what a bad representation it is of what typically goes wrong on an IC. By adding cell-aware and layout-aware diagnosis it is possible to get much better results. And by better, in the test world, that means more parts failing…on the tester as opposed to out in the real world. Mentor presented the technology in some detail at Sematech and I blogged about it here. Indeed, Mentor’s cell-aware ATPG was awarded the Semicon West “Best of the West” award, which is really the best of show award.

As a way to tempt you to take a look at this, I’ll recap that AMD did an experiment where they ran their normal manufacturing test for a part, then they took the chips that passed and ran them through Mentor’s cell-aware test. They got another 885 DPM failing. This is a huge number. If the chip ships 10M units, that is nearly 9000 systems that are not going to fail. Not all would necessarily make it out of the factory as failing systems, but it seems likely that some would. Everyone knows that the cost of a failure in the field is orders or magnitude more than detecting the failure earlier when it just means discarding a bad die.

There are also a number of presentations by Mentor’s customers.

- Toshiba on hybrid ATPG compression and LBIST together sharing test logic

- OnSemi on cell-aware test results in automotive

- LSI on cell-aware test results

- ASSET InterTech will have a demo and presentation in their booth showcasing interoperable IJTAG L/TAG flows

On Sunday, Mentor is running a tutorial on “Mixed-Signal DFT and BIST: Trends, Principles and Solutions.” Rumor has it that lots of people are signed up, so it is clearly a hot topic and likely to sell out.

ITC itself (and the exhibits) are September 10-12th, but there are tutorials on Sunday, and panels on Monday with a welcome reception in the evening.

Want to know more about Mentor at ITC, it is all here. Want to go to ITC, register here.

Comments

There are no comments yet.

You must register or log in to view/post comments.