Approximately 25% of SemiWiki traffic originates from search engines and the key search terms are telling. Since the beginning of SemiWiki, “low power design” has been one of the top searches. This is understandable since the mobile market has been leading us down the path to fame and fortune. Clearly lowering the power consumption of consumer products and networking centers is an important design consideration and this effort begins with the chips used in these devices.

Approximately 25% of SemiWiki traffic originates from search engines and the key search terms are telling. Since the beginning of SemiWiki, “low power design” has been one of the top searches. This is understandable since the mobile market has been leading us down the path to fame and fortune. Clearly lowering the power consumption of consumer products and networking centers is an important design consideration and this effort begins with the chips used in these devices.

Semiconductor design innovators like AMD wanted to improve on previous generation designs in terms of faster performance in a given power envelope, higher frequency at a given voltage, and improved power efficiency through clock gating and unit redesign.

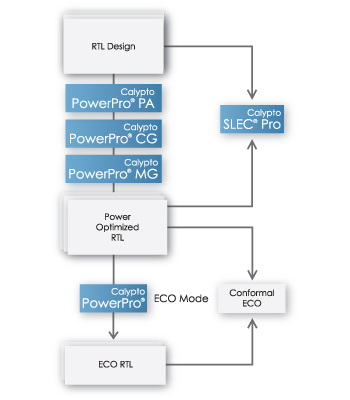

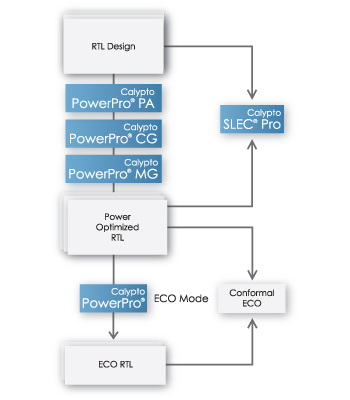

The AMD low-power core design team used a power analysis solution (PowerPro[SUP]®[/SUP] from Calypto[SUP]®[/SUP]) that helped analyze pre-synthesis RTL clock-gating quality, find opportunities for improvements, and generate reports that the engineering team could use to decrease the operating power of the design.

By targeting pre-synthesis RTL, power analysis can be run more often and over a larger number of simulation cycles — more quickly and with fewer machine resources than tools that rely on synthesized gates. The focus on clock gating and the quick turnaround of RTL analysis allowed AMD to achieve measurable power reductions for typical applications of a new, low-power X86 AMD core.

This article by Steve Kommrusch of AMD describes the power analysis methodology AMD used to improve clock-gating efficiency and identify key features and advantages that the tool delivered. Quantitative results are interpreted and presented in graphs and tables. Comparative data between PowerPro results and PTPX post-synthesis results, show that doing power analysis at the RTL stage rather than waiting until post-gate synthesis was very useful.

Ultimately, even given instructions per clock (IPC) and frequency improvements, PowerPro helped achieve an approximately 20% reduction in typical dynamic application power compared to an already-tuned low-power X86 CPU. You can read the whole article HERE.

Calypto Design Systems leads the industry in technologies for ESL hardware design and RTL power optimization. These technologies empower designers to create high quality and low power electronic systems for today’s most innovative electronic products.

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era