Embedded memories have an important impact on power. SoCs that integrate multiple functions on a single silicon die are at the heart of many electronic devices. As process geometries have scaled, design teams have used more and more of the additional silicon real estate available to integrate embedded memories that serve as scratch-pads, FIFOs, and caches to store data for the computational cores. As a result, most current designs have over 50 percent of their area used by embedded memories and these memories account for 50‑70 percent of total SoC power dissipation. Clearly, any attempt to reduce SoC power is incomplete if it does not attempt to reduce the power consumed by the embedded memories in a design.

Given the complexity of today’s SoCs, efficient power management requires a holistic approach where the control logic, data paths, and memories are analyzed together and optimized for both dynamic and static power. However, identifying sequential clock and memory gating opportunities is beyond the scope of RTL synthesis tools. Power conscious designers try to analyze the registers for redundant accesses and look for conditions under which such accesses can be shut off. There is no single known method of achieving this, and designers mostly develop this expertise over time. Even so, the process can get very tedious and error prone without suitable assistance.

In an earlier webinar Calypto presented the concept of deep sequential analysis (DSA) and how it can be used to reduce power at RTL. Sequential analysis involves temporal analysis of the complete design — including gates, flops, and memories — over several clock cycles and the examination of the stability, propagation, and observability of signal values. This is important for power optimization in identifying unused computations, data dependent functions, and don’t-care cycles in the original code.

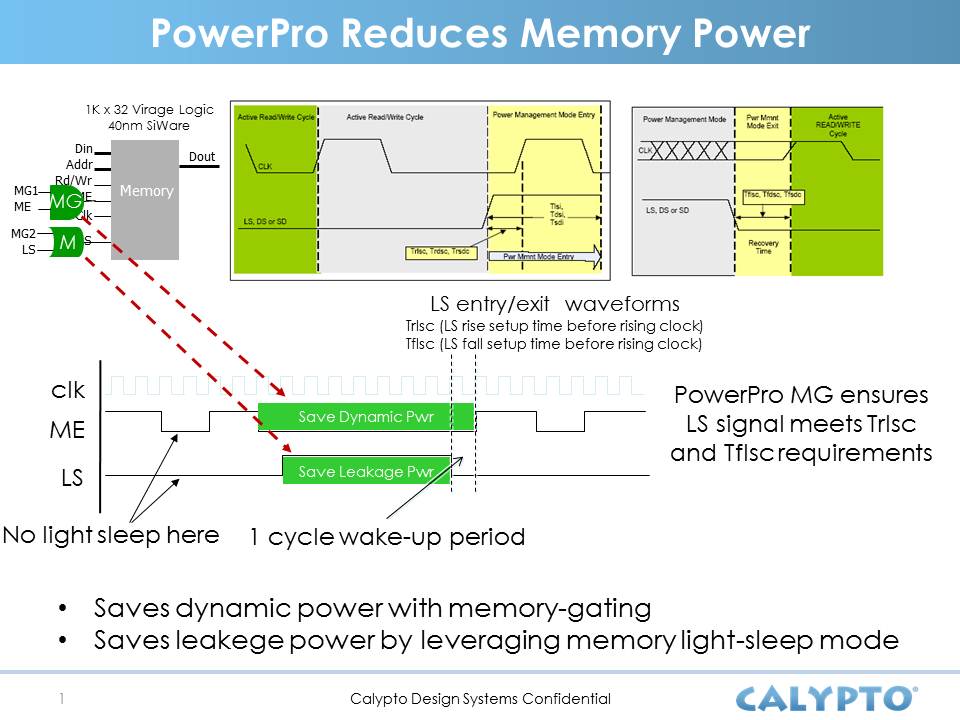

Sequential analysis is equally applicable to embedded memories. Memories are used to store the results of intermediate computations in the data pipelines; serve as buffers between interacting computations; or serve as caches to store frequently read data. Even though locally the reads and writes to a memory may appear to be necessary, depending on the functional mode or complex control sequence of the design, they may not be needed. Removing such redundant memory accesses can result in significant reduction in the dynamic power consumption of memories.

Memory vendors provide several capabilities to reduce leakage power in memories that are not in use, and various flavors of sleep modes are now available in embedded memories, but using these modes requires the creation of controllers to generate the sleep and wake signals. In addition, the leakage power savings gained during sleep mode must be greater than the dynamic power dissipation associated with transitioning the memory in and out of sleep mode. The memory must be in sleep mode for a minimum number of cycles to actually save power. Finally, creating the sleep mode control signals and ensuring that sleep modes are triggered only during periods when the memory is quiet for an extended period require analysis of the design functionality over multiple cycles. DSA is very effective in analyzing and identifying optimum sleep modes for embedded memories.

In their next webinar Calypto will show how its patented deep sequential analysis (DSA) technology can be applied to reduce memory power. Deep sequential analysis examines the read and write operation of memories over several cycles and automatically optimizes the memories for both dynamic and leakage power. It also implements optimized sleep modes for the memory.

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center