Little known fact, SpringSoft, Inc. is the largest supplier of EDA software in Asia with headquarters in both Hsinchu, Taiwan, and in Silicon Valley, CA. You will be hard pressed to find a company that does not use SpringSoft products and being located right down the street from the top two foundries doesn’t hurt either.

Little known fact, SpringSoft, Inc. is the largest supplier of EDA software in Asia with headquarters in both Hsinchu, Taiwan, and in Silicon Valley, CA. You will be hard pressed to find a company that does not use SpringSoft products and being located right down the street from the top two foundries doesn’t hurt either.

SpringSoft’s products include the ever popular Novas line of verification enhancement solutions, and the Laker line of custom IC design solutions. These solutions share the common characteristic that they automate tedious, time consuming tasks to allow engineers to focus on activities that add value. SpringSoft customers include all of the top fabless semiconductor companies and all of the IDMs and the top foundries. That combined customer experience is extremely hard to come by!

You can tell a lot about an EDA company by their DAC 2012 plan. Clearly SpringSoft has been busy with both customers and partners. I have spent time with SpringSoft as a partner and can tell you they are very collaborative and a pleasure to work with. SpringSoft has also been with SemiWiki since the beginning, see their landing page HERE, lots of good stuff by Paul McLellan.

SpringSoft Activities at DAC

SpringSoft is focused on delivering innovative technologies to address critical challenges in the development of complex digital, analog and mixed-signal designs. Our award-winning products enable engineers to speed debug, improve functional verification quality, and create optimal custom IC designs.

Product demonstrations

Verdi[SUP]3[/SUP]™ Automated Debug Platform At DAC in 2012, SpringSoft will show the latest generation of its flagship debug product, Verdi[SUP]3[/SUP], which has been streamlined and optimized to address the increasing complexity and new methodologies you are facing today. In addition, there will be demonstrations of the new Verdi Interoperability Apps (VIA).See how VIA can help you to create and interface your own applications with the Verdi platform. SpringSoft and a number of our VIA partners will demonstrate ways to extend the functionality of Verdi and to combine it with partner tools. Click here for more info.

Certitude™ Functional Qualification System The Certitude Functional Qualification System is the only solution to provide an objective measure of the quality of your verification environment and guidance on how to improve it. Certitude injects potential bugs into your design and evaluates the ability of your verification environment to catch them. It completely analyzes whether the potential bugs are activated, propagated to observable outputs, and detected by your environment, thus identifying whether you need to improve your tests, assertions or checkers. Click here for more info.

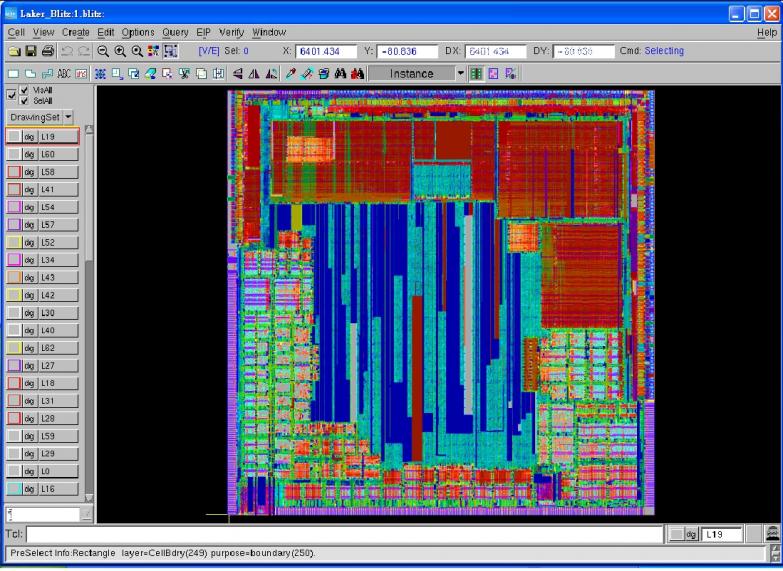

Laker[SUP]3[/SUP]™ Custom IC Design platformSpringSoft’s new Laker platform, just announced in April 2012, is a major product update of the popular Laker product family that enables the design of analog, mixed-signal, and custom digital chips with superior productivity and unmatched interoperability.The Laker showcase at this year’s DAC will feature the new Laker Analog Prototyping, the latest addition to the Laker family that automates the process of analyzing advanced process effects and generating constraints to guide circuit layout. Its unique capabilities enable automated constraint generation, layout exploration, and rapid implementation in a single flow. Click here for more info.

ProtoLink Probe Visualizer Let us show you how you can accelerate FPGA prototype bring-up, capture 1000s of signals up to 1 sec of emulation time, probe ECO to add signals in minutes and debug at system level across multiple FPGAs with Verdi. Click here for more info.

Featuring Next Generation Hierarchical Timing Technology – HyperScale

Date:Monday,June 4, 2012

Time:6:00 – 08:30pm

Location:San Francisco Marriott Marquis, Golden Gate Ballroom A

Address:55 4th Street San Francisco, CA 94103

Registration: http://www.synopsys.com/cgi-bin/ptsig12dc/reg1.cgi

IPL Luncheon workshop

Reaping the Benefits of iPDKs

Date:Tuesday, June 5th, 2012

Time:12:00pm-1:30pm

Location:San Francisco Marriott Marquis, Golden Gate Ballroom A

Address:55 4th Street San Francisco, CA 94103

Registration: http://www.iplnow.com/cgi-bin/ipl_lunch/reg1.cgi

Interoperable PDKs (iPDKs) benefit the entire custom design ecosystem. Semiconductor foundries and IDMs create iPDKs to reduce their PDK development, validation, support and distribution costs while enabling advanced design flows and multiple EDA tool support. All leading foundries today are delivering iPDKs. Chip designers now enjoy access to best-in-class tools, interoperable flows, and improved productivity. At the 6th Annual IPL Luncheon, presenters from multiple foundries will highlight the benefits of iPDK standard and their experiences in developing and deploying foundry iPDKs. The IPL Alliance will present an update on the current and future IPL projects.

Accellera Hosted Luncheon and Technical Presentation

Accellera Systems Initiative Rolls Out the Unified Coverage Interoperability Standard

Date:Wednesday, June 6th, 2012

Time:12:00pm-1:30pm

Location:Moscone Center, Room 262

Registration: http://www.accellera.org/news/events/dac_lunch_2012/event_registration/

Coverage metrics are critical to measuring and guiding design verification. As designs have grown, increasingly advanced verification technologies, methods and additional metrics have been designed to form a fuller coverage model. There is currently no single metric that consistently and globally tells engineers the exact status of verification. But one step in the right direction is to bring all types of coverage metrics into a single database that can be accessed in an industry standard way. The UCIS facilitates the creation of a unified coverage database that allows for interoperability of coverage data across multiple tools from multiple vendors.

This presentation, intended for verification managers and tool developers alike, provides an introduction to and overview of the UCIS and how users plan to utilize it to enhance their verification flows. We provide a survey of many of the commonly-used coverage metrics and how they are modeled in the UCIS. The information that users will be able to access through the UCIS will allow them to write their own applications to analyze, grade, merge and report coverage from one or more databases from one or more tool vendors. We will also discuss the XML-based interchange format of UCIS, which provides a path to exchange coverage databases without requiring a common code library between tools and vendors. Click here for more details.

LDE Aware Design Solution in Advanced Technologies

Date:Tuesday, June 5th, 2012

Time:12:30pm-1:30pm

Location:Room 105 – exhibit floor

User Track #2 – Paper 2.25: LDE Aware Design Solution in Advanced Technologies

M.J. Huang, Sharon Jiang, Steven Chen – Taiwan Semiconductor Manufacturing Co., Ltd., Hsinchu, Taiwan

Cliff Hung, Captain Liu – SpringSoft, Inc., Hsin-chu, Taiwan

To schedule a meeting or private in-depth demo, please contact your sales representitive or e-mail us at DAC2012@springsoft.com.

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center