Managing and controlling thermal conditions in-chip is nothing new and embedded temperature monitoring has been going on for many years. What is changing however, is the granularity and accuracy of the sensing now available to SoC design teams. Thermal activity can be quite destructive and if not sufficiently monitored can … Read More

Staying on the Right Side in Worst Case Conditions – Performance (Part 2)

In this, the second part of a two-part series we delve further into defining worst case, this time focusing specifically on device performance.

In the last blog we talked about the steady increase in power density per unit silicon area and how worst case is definitely getting worse. We discussed how in each new FinFET node the dynamic… Read More

Talking Sense with Moortec: Staying on the right side in worst case conditions – Power (Part 1)

In this first part of a 2-part blog series, we look at defining worst case conditions, focusing specifically on device power.

With great power, comes great responsibility…

With each new technology node especially FinFET, the dynamic conditions within a chip are changing and becoming more complex in terms of process speeds, thermal… Read More

Fractal CEO Update 2020

Rene Donkers, the company’s Co-founder and CEO, started his EDA career at Sagantec where he became responsible for world wide customer support and operations management. Ten years ago, Rene and a handful of people noticed a need in the design community for a standardized (portable) IP Validation approach to replace internal… Read More

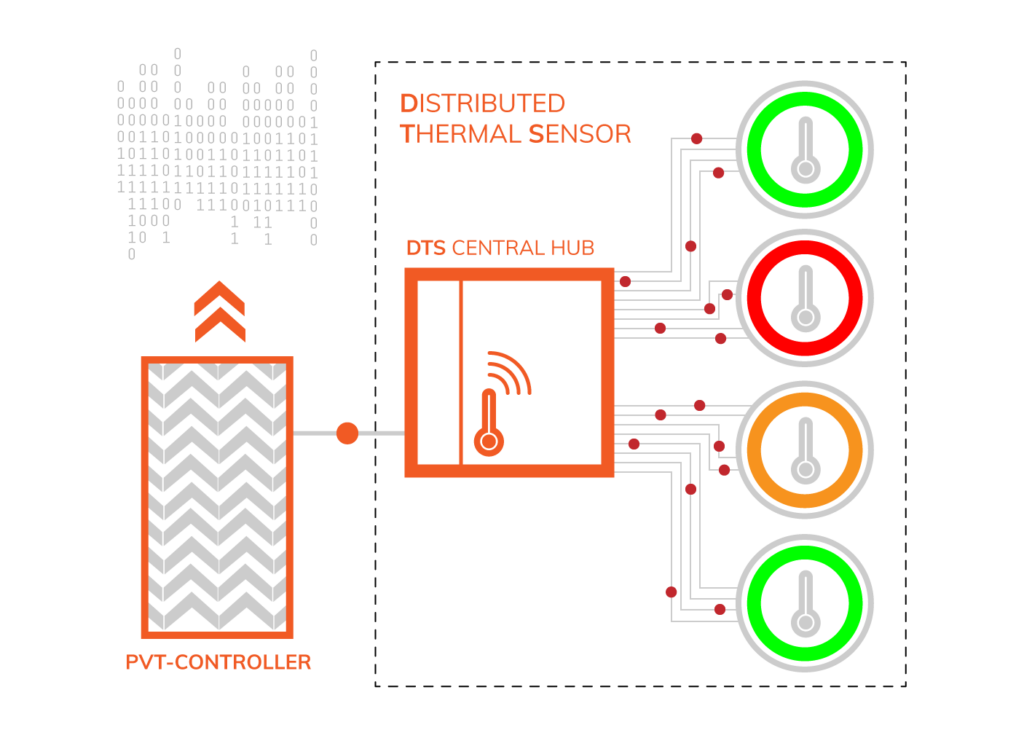

Moortec Delivers Distributed, Real-Time Thermal Sensing on TSMC N5 Process

Moortec is known for its innovative in-chip monitoring and sensing products. They’re based in the UK and have been delivering this kind of embedded technology since 2010. Dan Nenni covered an overview of the company recently. SemiWiki also hosted a webinar about optimizing power and increasing data throughput in AI from Moortec… Read More

Talking Sense With Moortec…Speak No Evil!

In the first of this blog trilogy, Talking Sense with Moortec…’Are you listening’, I looked at not waiting for hindsight to be wise after the event, instead make use of what’s available and act ahead of time. In the second, Talking Sense with Moortec…’See no evil’, we bizarrely saw how Sir Francis Drake, Admiral Nelson and Clint… Read More

Talking Sense With Moortec…See No Evil!

In the first of this blog trilogy, Talking Sense with Moortec…’Are you listening’, I looked at not waiting for hindsight to be wise after the event, instead make use of what’s available and act ahead of time.

There’s a Japanese maxim, depicting three ‘wise’ monkeys… Kikazaru, Mizaru, and Iwazaru, better known as ‘hear no evil, … Read More

Talking Sense With Moortec…Are You Listening?!

It almost doesn’t matter what your job may be, whether in the public sector or a private company, or how technical or how dangerous, many of life’s adages and sayings can be interpreted to have some direct meaning for all of us.

Over the years in our personal lives, we have been constantly advised that prevention is better than cure…certainly… Read More

Webinar: Real-time In-Chip Monitoring to Boost multi-core AI, ML, DL Systems

During the COVID-19 pandemic I’m using Zoom and attending more webinars to keep updated on semiconductor industry trends, and one huge trend is the importance of AI applied to SoCs. Using more cores to handle ML and DL makes sense, but then how do you keep the chips within their power and reliability limits while at the same … Read More

Key Applications for Chip Monitoring

One of the side benefits of working with SemiWiki is that you get to meet a broad range of people and in the semiconductor industry that means a broad range of very smart people, absolutely. Recently I had the pleasure to meet Richard McPartland of Moortec. Richard and I started in the semiconductor industry at the same time but from… Read More