Given that SoC design today is predicated on IP reuse, you would assume that processes to deliver, maintain and communicate status on reusable IP should be highly optimized. But that’s not necessarily the case, especially when so many design companies have consolidated, each brings its own IP libraries, design flows, license… Read More

Jump Start your Secure IoT Design with Intrinsix

Have you ever had a great idea for a new product but then stopped short of following through on it because of the complexities involved to implement it? It’s frustrating to say the least. It is especially frustrating, when the crux of your idea is simple, but complexity arises from required components that don’t add to the functionality… Read More

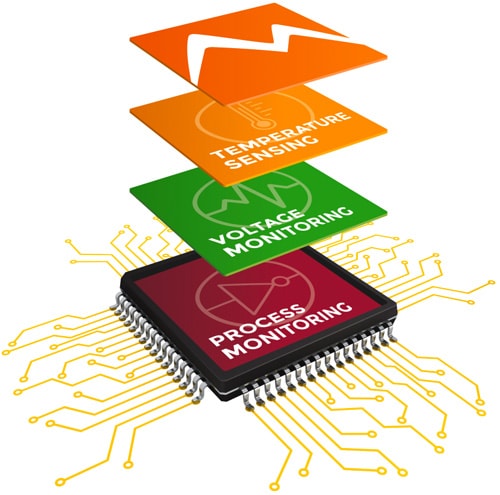

Making Your Next Chip Self-Aware

One holy grail of AI software developers is to create a system that is self-aware, or sentient. A less lofty goal than sentient AI is for chip designers to know how each specific chip responds to Process variations, Voltage levels and Temperature changes. If a design engineer knew exactly which process corner that each chip was fabricated… Read More

Outsourced Operations: Reduced Risk, Fast Ramp, and Managed Complexity

One of the more interesting semiconductor success stories is Apple and how they transformed from a struggling computer company to a dominant chip maker. We covered this story in quite a bit of detail in our book “Mobile Unleashed” in Chapter 7 “From Cupertino” but the short answer to how they did it is: Outsourced Operations.

Apple’s… Read More

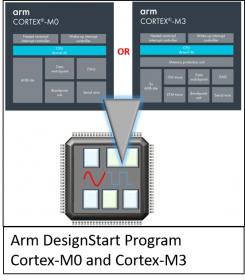

Arm and Mentor Use DesignStart Program to Accelerate Proof-of-Concept for IoT Designs

Sometimes the hardest thing about bringing a new idea to fruition is overcoming the inertia to get started with a proof-of-concept. You must be able to put together enough parts of the solution to prove to those controlling budgets that an idea has merit and is worth taking to the next level. It’s a bit of a chick-vs-egg scenario as … Read More

Finding the Right Needle in the IP Haystack

As the percentage of pre-configured IP increases in semiconductors, so design teams are able to reduce design cycle times. But one of the challenges for design teams is the inability to quickly and easily find IP because it’s incorrectly classified, sat in a designer’s home directory, or it’s been put into the ‘repository’ by an… Read More

1st Annual International Conference, Semiconductors ISO 26262

When we talk about the promise of ADAS and autonomous cars then along the way we also hear about this functional safety standard called ISO 26262 which semiconductor companies all pay close attention to. I recently learned about a new conference called Semiconductors ISO 26262, scheduled for December 5-7 in Munich, Germany. The… Read More

Software Defined Networks (on Chip) – NetSpeed Systems and UltraSoC Team Up to Use Embedded Analytics to Enable Next Generation SoCs

NetSpeed Systems is known for their network-on-chip (NoC) IP that enables complex heterogeneous SoC architectures. NetSpeed IP supports both non-coherent and coherent memory and I/O schemes as well as configurable, customized last level cache optimization through their Orion, Gemini and Pegasus IP respectively. They are… Read More

Good Library Hygiene Takes More Than an Occasional Scrub

You don’t shower only before you have to go to an important meeting (teenagers excepted). Surgical teams go further, demanding a strict regimen of hygiene be followed before anyone is allowed into an operating room. Yet we tend to assume that libraries and physical IP (analog, memories, other physical blocks) are checked and pronounced… Read More

IoT Security Hardware Accelerators Go to the Edge

Last month I did an article about Intrinsix and their Ultra-Low Power Security IP for the Internet-of-Things (IoT). As a follow up to that article, I was told by one of my colleagues that the article didn’t make sense to him. The sticking point for him, and perhaps others (and that’s why I’m writing this article) is that he couldn’t … Read More